PM0214 Rev 9 237/262

PM0214 Core peripherals

261

4.4.10 Configurable fault status register (CFSR; UFSR+BFSR+MMFSR)

Address offset: 0x28

Reset value: 0x0000 0000

Required privilege: Privileged

The following subsections describe the subregisters that make up the CFSR:

• Usage fault status register (UFSR) on page 238

• Bus fault status register (BFSR) on page 239

• Memory management fault address register (MMFSR) on page 240

The CFSR is byte accessible. You can access the CFSR or its subregisters as follows:

• Access the complete CFSR with a word access to 0xE000ED28

• Access the MMFSR with a byte access to 0xE000ED28

• Access the MMFSR and BFSR with a halfword access to 0xE000ED28

• Access the BFSR with a byte access to 0xE000ED29

• Access the UFSR with a halfword access to 0xE000ED2A.

The CFSR indicates the cause of a memory management fault, bus fault, or usage fault.

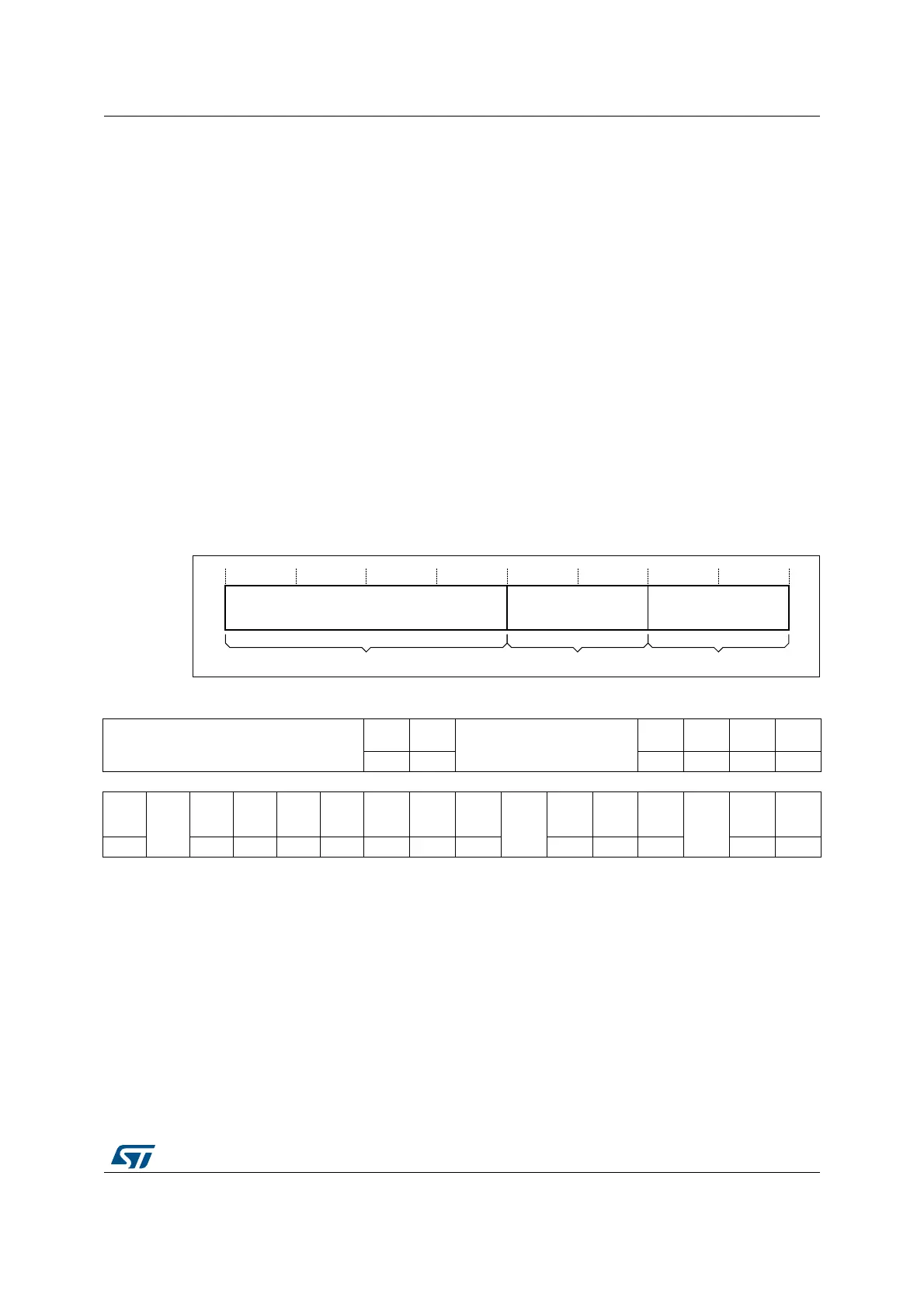

Figure 20. CFSR subregisters

0HPRU\0DQDJHPHQW

)DXOW6WDWXV5HJLVWHU

8VDJH)DXOW6WDWXV5HJLVWHU

%XV)DXOW6WDWXV

5HJLVWHU

8)65 %)65 00)65

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

DIVBY

ZERO

UNALI

GNED

Reserved

NOCP INVPC

INV

STATE

UNDEF

INSTR

rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1

1514131211109876543210

BFARV

ALID

Reserv

ed

LSP

ERR

STK

ERR

UNSTK

ERR

IMPRE

CIS

ERR

PRECI

S ERR

IBUS

ERR

MMAR

VALID

Reserv

ed

MLSP

ERR

MSTK

ERR

M

UNSTK

ERR

Res.

DACC

VIOL

IACC

VIOL

rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 UFSR: see Usage fault status register (UFSR) on page 238

Bits 15:8 BFSR: see Bus fault status register (BFSR) on page 239

Bits 7:0 MMFSR: see Memory management fault address register (MMFSR) on page 240

Loading...

Loading...