PM0214 Rev 9 39/262

PM0214 The Cortex-M4 processor

261

For an asynchronous exception other than reset, the processor can execute another

instruction between when the exception is triggered and when the processor enters the

exception handler.

Privileged software can disable the exceptions that Table 17 on page 38 shows as having

configurable priority. For further information, see:

• System handler control and state register (SHCSR) on page 235

• Interrupt clear-enable register x (NVIC_ICERx) on page 211

For more information about hard faults, memory management faults, bus faults, and usage

faults, see Section 2.4: Fault handling on page 44.

2.3.3 Exception handlers

The processor handles exceptions using:

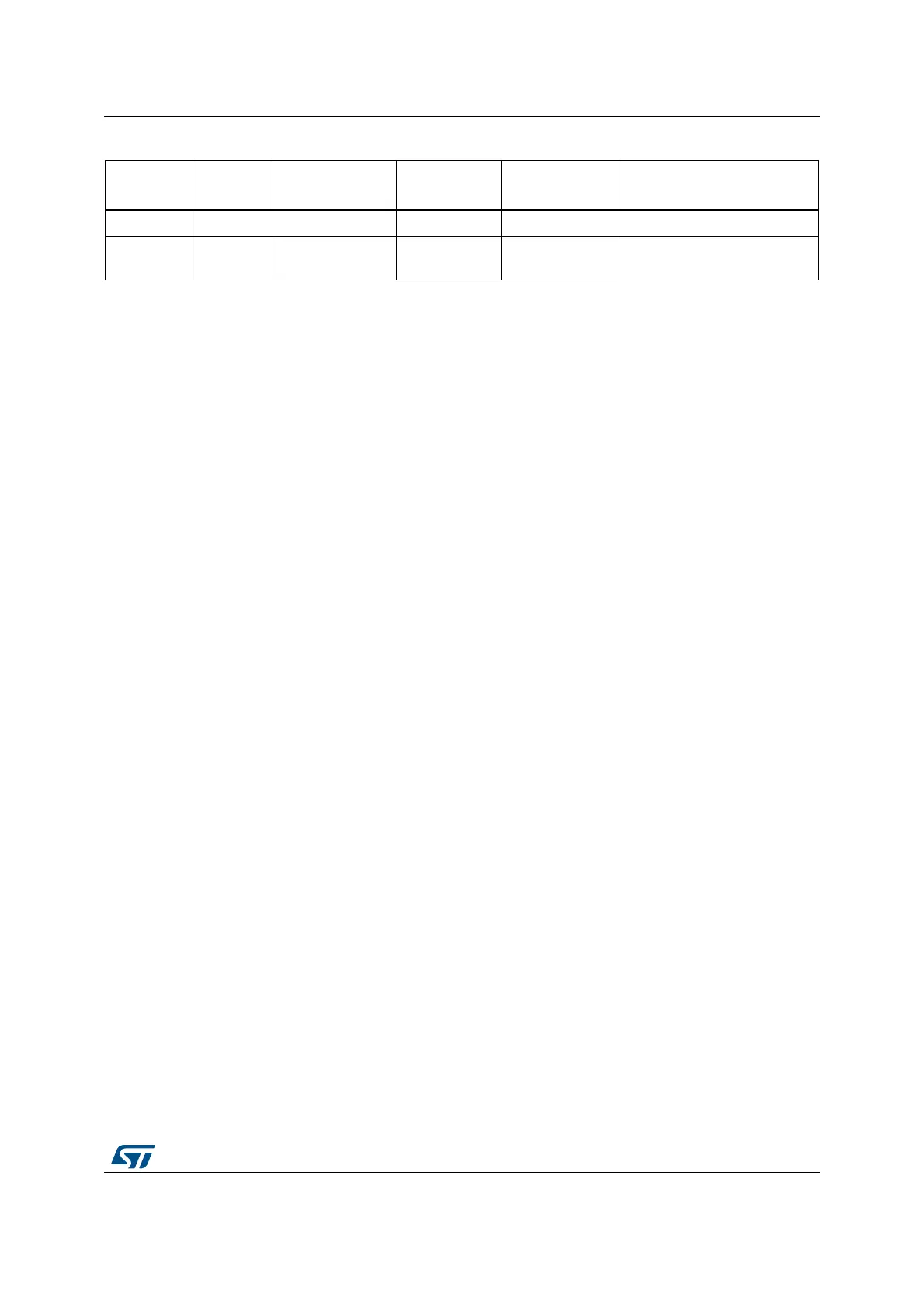

15 -1 SysTick Configurable

(3)

0x0000003C Asynchronous

16 and

above

0 and

above

Interrupt (IRQ) Configurable

(4)

0x00000040 and

above

(5)

Asynchronous

1. To simplify the software layer, the CMSIS only uses IRQ numbers and therefore uses negative values for exceptions other

than interrupts. The IPSR returns the Exception number. For further information see Interrupt program status register on

page 22.

2. See Vector table on page 40 for more information.

3. See System handler priority registers (SHPRx) on page 233.

4. See Interrupt priority register x (NVIC_IPRx) on page 215.

5. Increasing in steps of 4.

Table 17. Properties of the different exception types (continued)

Exception

number

(1)

IRQ

number

(1)

Exception

type

Priority

Vector address

or offset

(2)

Activation

Interrupt Service

Routines (ISRs)

Interrupts IRQ0 to IRQ81 are the exceptions handled by ISRs.

Fault handlers Hard fault, memory management fault, usage fault, bus fault are fault

exceptions handled by the fault handlers.

System handlers NMI, PendSV, SVCall SysTick, and the fault exceptions are all

system exceptions that are handled by system handlers.

Loading...

Loading...