PM0214 Rev 9 257/262

PM0214 Core peripherals

261

4.6.5 Floating-point default status control register (FPDSCR)

Address offset: 0x0C

Reset value: 0x0000000

Required privilege: Privileged

The FPDSCR register holds the default values for the floating-point status control data.

4.6.6 Enabling the FPU

The FPU is disabled from reset. You must enable it before you can use any floating-point

instructions.

The example shows an example code sequence for enabling the FPU in both privileged and

user modes. The processor must be in privileged mode to read from and write to the

CPACR.

Example

; CPACR is located at address 0xE000ED88

LDR.W R0, =0xE000ED88

; Read CPACR

LDR R1, [R0]

; Set bits 20-23 to enable CP10 and CP11 coprocessors

ORR R1, R1, #(0xF << 20)

; Write back the modified value to the CPACR

STR R1, [R0]; wait for store to complete

DSB

;reset pipeline now the FPU is enabled

ISB

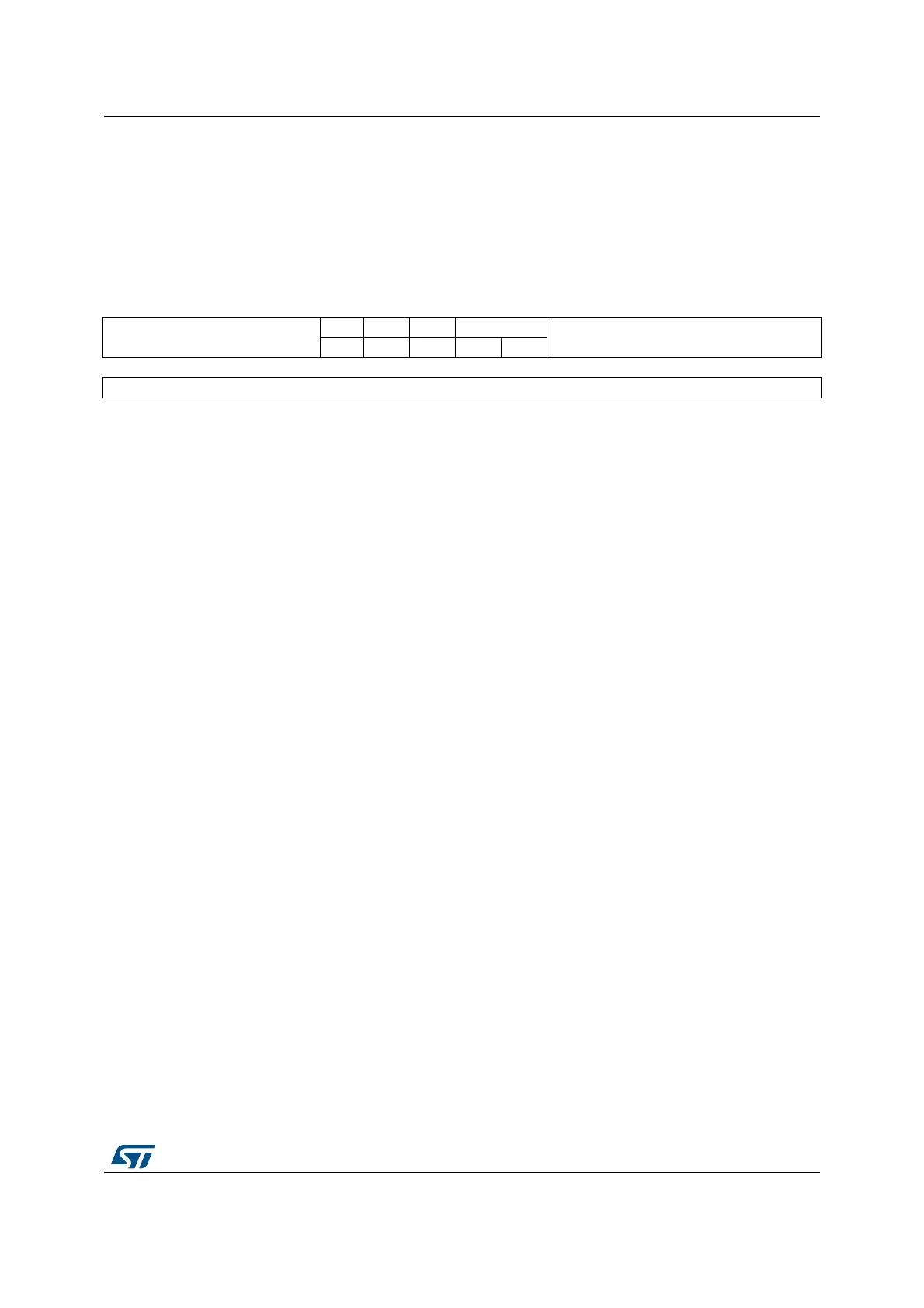

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

AHP DN FZ RMode

Reserved

rw rw rw rw rw

1514131211109876543210

Reserved

Bits 31:27 Reserved, must be kept cleared.

Bit 26 AHP: Default value for FPSCR.AHP

Bit 25 DN: Default value for FPSCR.DN

Bit 24 FZ: Default value for FPSCR.FZ

Bits 23:22 RMode: Default value for FPSCR.RMode

Bits 21:0 Reserved, must be kept cleared.

Loading...

Loading...