PM0214 Rev 9 227/262

PM0214 Core peripherals

261

4.4.4 Vector table offset register (VTOR)

Address offset: 0x08

Reset value: 0x0000 0000

Required privilege: Privileged

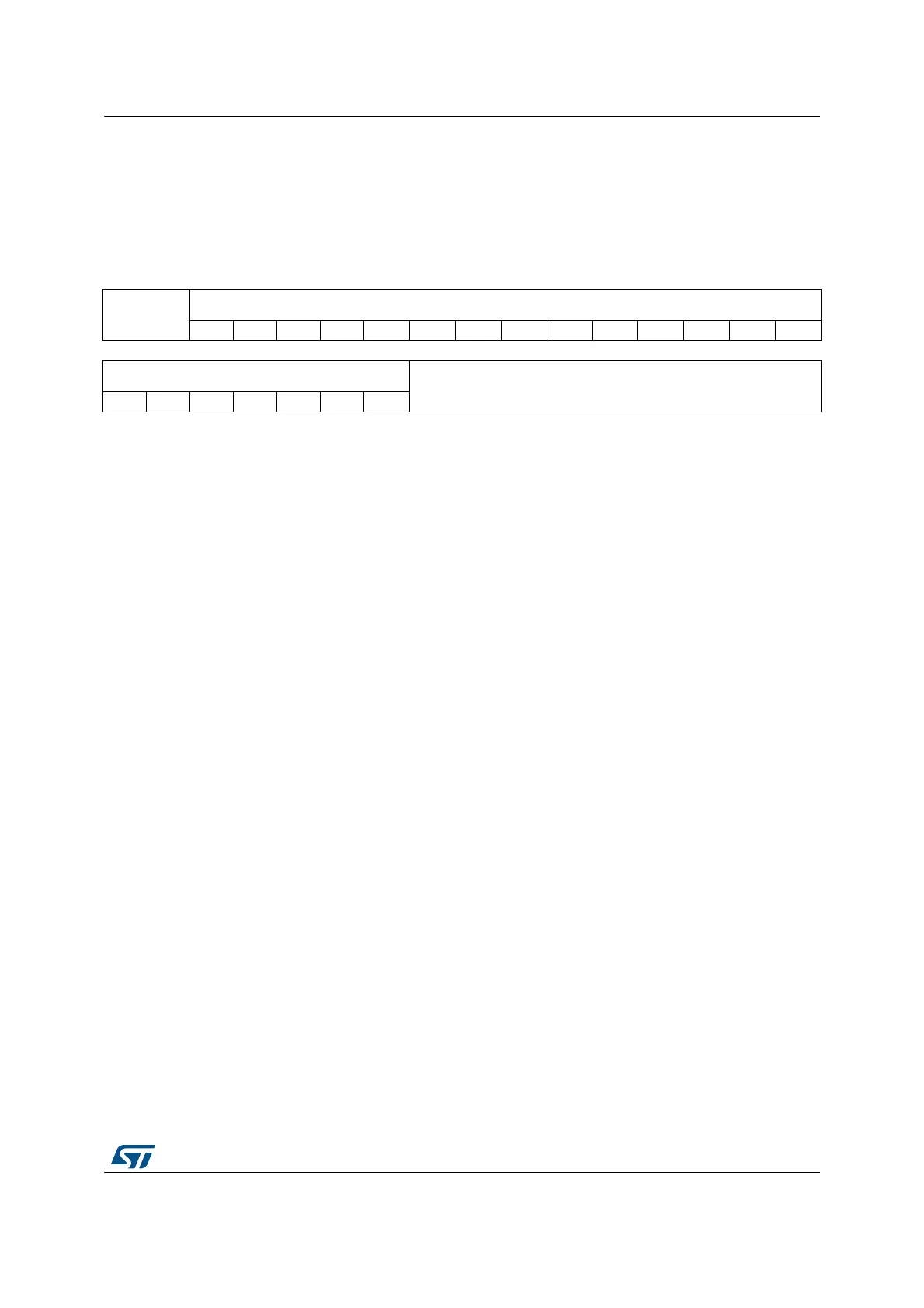

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

TBLOFF[29:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

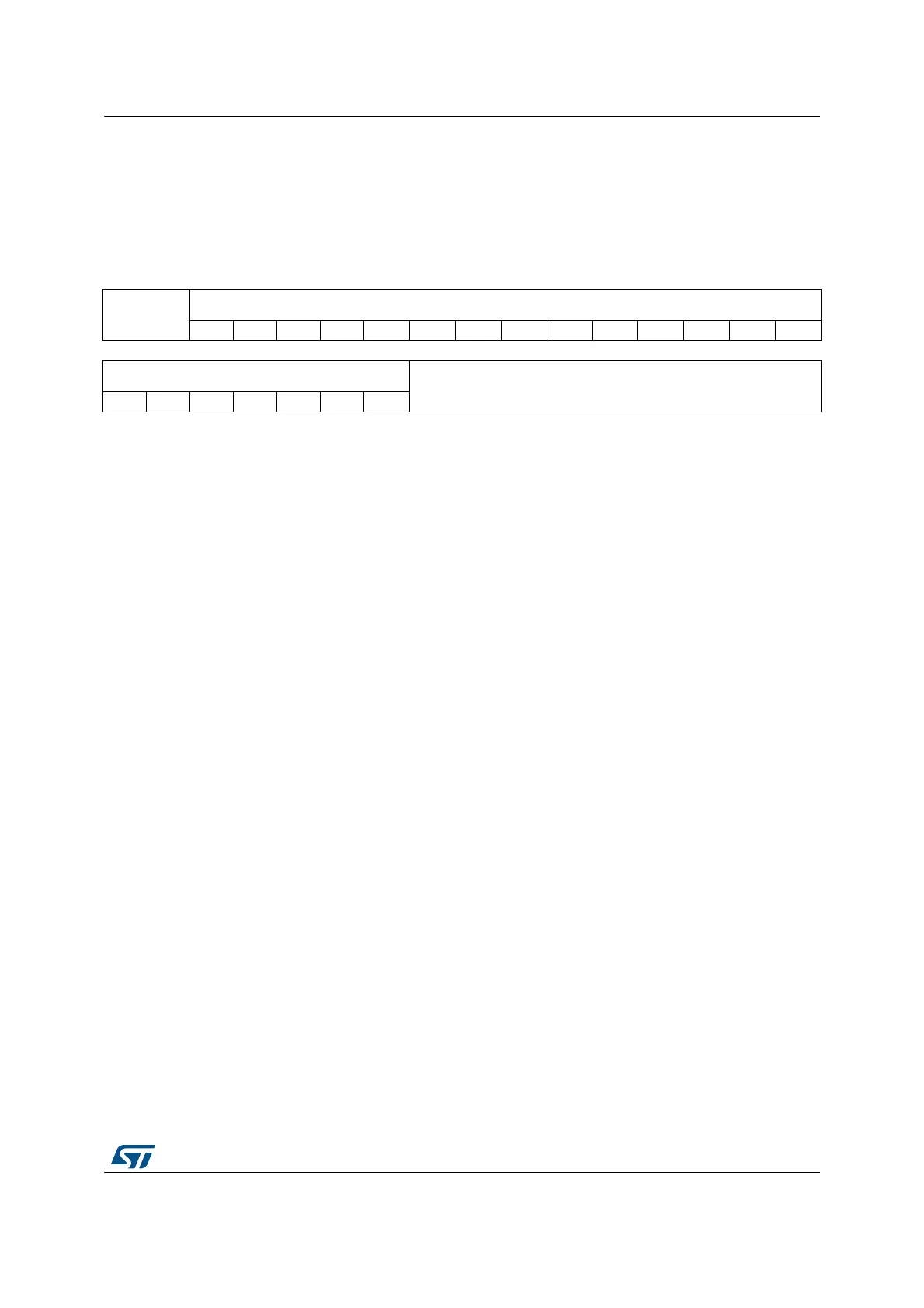

1514131211109876543210

TBLOFF[15:9]

Reserved

rw rw rw rw rw rw rw

Bits 31:30 Reserved, must be kept cleared

Bits 29:9 TBLOFF: Vector table base offset field.

It contains bits [29:9] of the offset of the table base from memory address 0x00000000. When

setting TBLOFF, you must align the offset to the number of exception entries in the vector

table. The minimum alignment is 128 words. Table alignment requirements mean that bits[8:0]

of the table offset are always zero.

Bit 29 determines whether the vector table is in the code or SRAM memory region.

0: Code

1: SRAM

Note: Bit 29 is sometimes called the TBLBASE bit.

Bits 8:0 Reserved, must be kept cleared

Loading...

Loading...