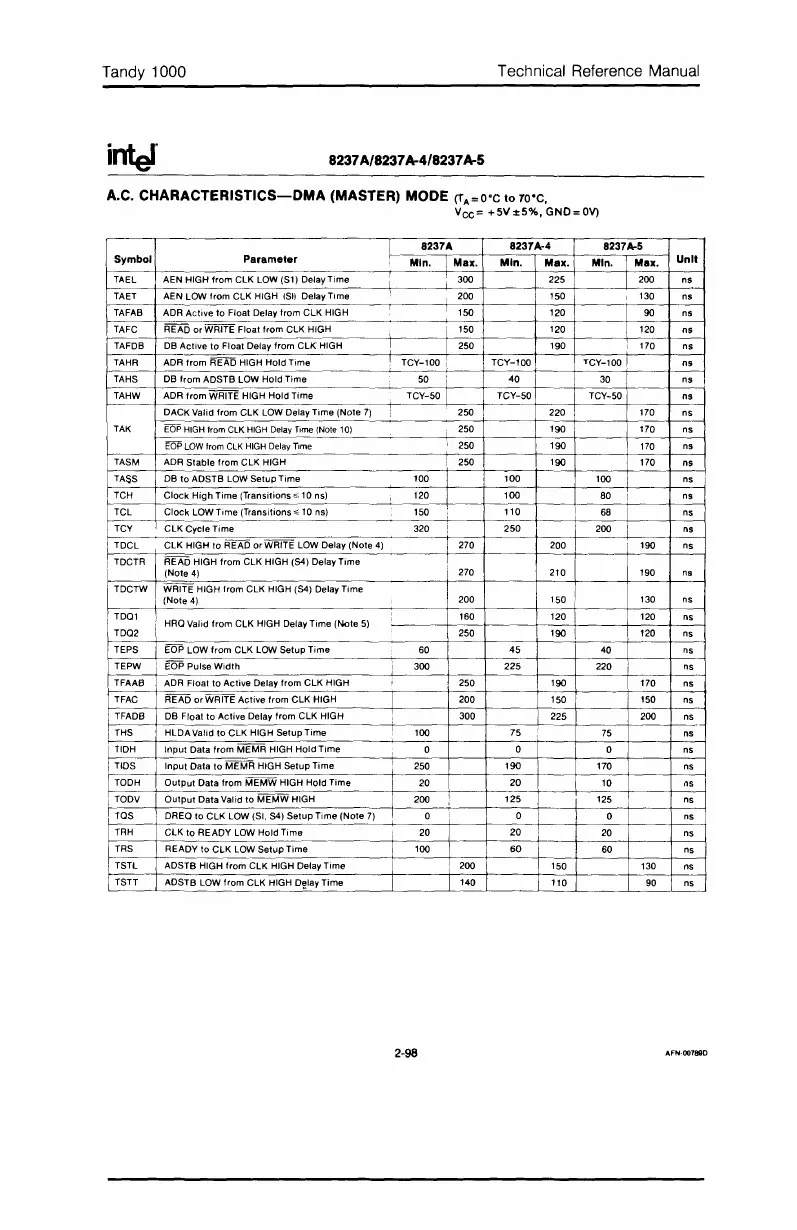

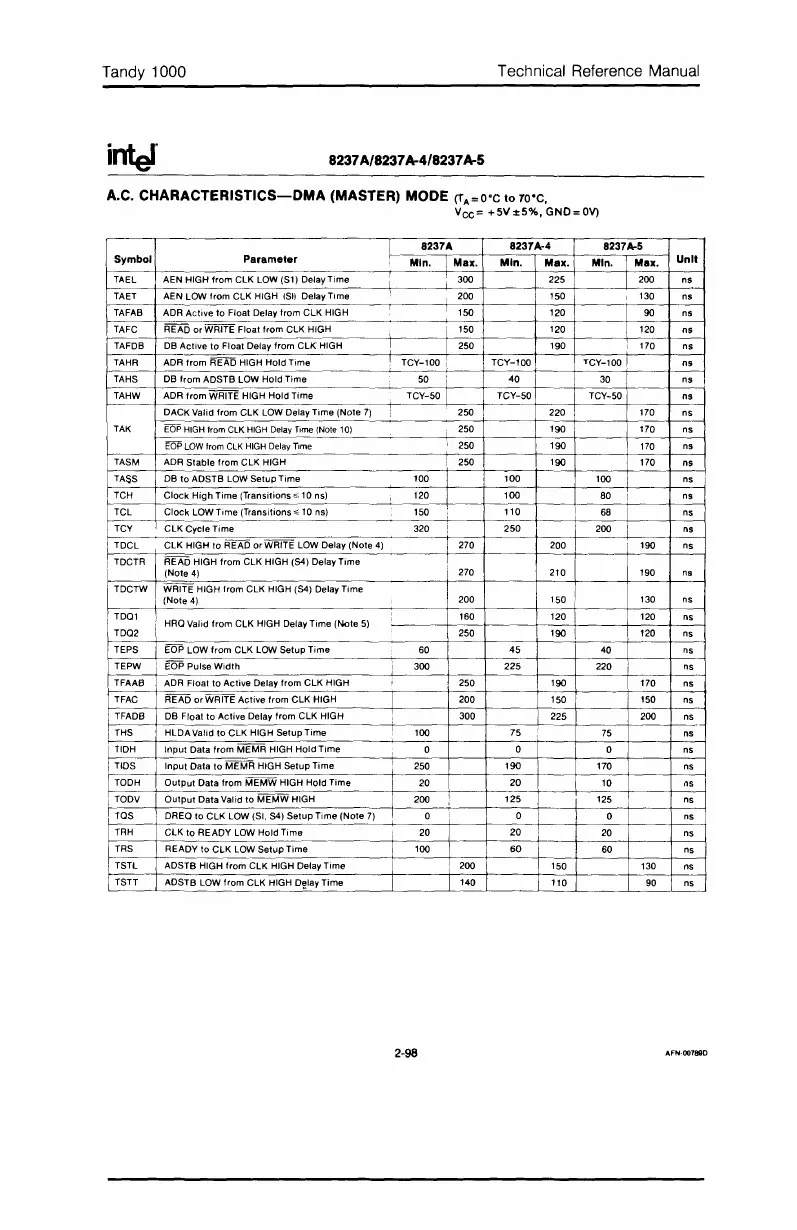

Tandy 1000

8237A/8237~4/8237~5

Technical Reference Manual

A.C.

CHARACTERISTICS-DMA

(MASTER) MODE (TA=O·C to

WC,

v

cc

=

+5V:t:5%,

GND=OVj

8237A 8237A-4

8237A-5

Symbol Parameter

Min. Max.

Min.

Max. Min.

Max.

Unit

TAEL AEN HIGH from CLK

LOW

(S1) DelayTime

: :

300 225 200

ns

TAET

AEN LOW from CLK HIGH

lSI)

DelayTime

!

200 150

I

130 ns

TAFAB

ADR Active to Float Delay from CLK HIGH

150

120

90

ns

TAFC READ or WRITE Float from CLK HIGH

i

150 120 120

ns

TAFDB DB Active to Float Delay from CLK' HIGH

I

I

250 190 170

ns

TAHR

ADR

from READ HIGH Hold Time

TCY-l00

TCY-100

TCY-l00

I

ns

TAHS

DB from ADSTB

LOW

Hold Time

50

i

40

30 ns

TAHW

ADR

from WRITE HIGH Hold Time TCY-50 TCY-50 TCY-50

ns

DACK Valid from CLK LOW Delay Time (Note

7)

250 220 170 ns

TAK

EOP

HIGH

from

ClK

HIGH

Delay

Time

(Note

10)

I

250 190 170 ns

EOP

LOW

from

ClK

HIGH

Delay

Time

250

190

170

ns

I TASM

ADR

Stable from CLK HIGH 250 190 170

ns

TASS DB to ADSTB LOW Setup Time

100

100

100 ns

TCH

Clock High Time (Transitions", 10 ns) 120 100

80

I

ns

TCL Clock LOW Time

(Transitions'" 10 ns) 150

110

I

68 ns

TCY CLK Cycle Time 320

I

250

200 ns

TDCL CLK HIGH to READ orWRITE LOW Delay (Note

4)

270

200 190 ns

I TDCTR

READ HIGH from CLK HIGH (54) Delay Time

(Note

4)

270

210 190

ns

TDCTW WRITE HIGH from CLK HIGH (54) Delay Time

(Note

4)

,

200 150

130 ns

TD01

! HRO Valid from CLK HIGH Delay Time (Note

5)

160 120 120

ns

TD02

i

250

190

120

ns

TEPS EOP LOW from CLK

LOW

Setup Time

.

60

45

40 ns

TEPW EOP Pulse Width

I 300

225

220 ns

TFAAB

ADR

Float

to

Active Delay from CLK HIGH 250

190 170 ns

TFAC READ orWRITE Active from CLK HIGH 200

150

150

ns

TFADB DB Float to Active Delay from CLK HIGH

]

300

225

200

ns

I THS

HLDAValid to CLK HIGH Setup Time

I

100

75

75

ns

TIDH Input Data from MEMR HIGH Hold Time

0

0

0

ns

liDS

Input Data to MEMR HIGH Setup Time

250 190 170 ns

TODH

Output

Data from MEMW HIGH Hold Time

20

20

10

os

TODV

Output

Data Valid to MEMW HIGH

200

125

125 ns

TOS

DR

EO to CLK LOW (SI, 54) Setup Time (Note

7)

0

0

0

ns

TRH

CLK

to

READY

LOW

Hold Time

20

20

20

ns

TRS

READY to CLK LOW Setup Time 100

60

60 ns

TSTL

ADSTB HIGH from CLK HIGH Delay Time

I

200

150 130

ns

TSTT

ADSTB LOW from CLK HIGH

D~lay

Time 140

110

90

ns

2-98

AFN-00189D

Loading...

Loading...