Tandy 1000

MC6845

PIN

DESCRIPTION

Technical Reference Manual

PROCESSOR INTERFACE

The

CRTC interfaces

to

a processor bus

on

the

bidirectional data bus

(00·07)

using

CS,

RS,

E,

and RIW

for

control

signals.

Data Bus

(00-07)

-

The

bidirectional data lines

(00·07)

allow

data

transfers between

the

CRTC internal

Register File and

the

processor. Data bus

output

drivers

are 3-state buffers which remain

in

the

high impedance

state

except

when

the

processor performs a CRTC read

operation.

A high level

on

a

data

pin

is

a

logical"

1."

Enable (EI -

The

Enable signal

is

a high impedance

TTL/MOS

compatible

input

which enables

the

data bus

input/output

buffers and clocks data

to

and

from

the

CRTC. This signal

is

usually derived from

the

processor

clock, and

the

high

to

low transition

is

the

active edge.

Chip Select

(CS)

- The

CS

line

is

a high impedance

TTL/MOS

compatible

input which selects

the

CRTC when

low

to

read

or

write

the

internal Register File. This signal

should

only

be active when there

is

a valid stable address

being decoded from

the

processor.

Register Select (RSI - The

RS

line

is

a high impedance

TTL/MOS

compatible

input which selects

either

the

Address

Register

(RS =

"0")

or

one of

the

Data Registers

(RS

=

"1"1

of

the

internal Register File.

ReadlWrite

(RM)

- The RIW line

is

a high impedance

TTL/MOS

compatible

input

which determines.

whether

the

internal Register File gets

written

or

read. A write

is

active low

("0").

CRT CONTROL

The CRTC provides horizontal sync (HSI, vertical sync

(VS), and Display Enable signals.

Vertical

Sync

(V

SYNC) - This TTL

compatible

output

is

an active high signal

which

drives

the

monitor

directly

or

is

fed

to

Video Processing

logic

for

composite

generation. This signal determines

the

vertical position of

the

displayed text.

Horizontal

Sync

(H

SYNC) - This

TTL

compatible

output

is

an active high signal

which

drives

the

monitor

directly

or

is

fed

to

Video Processing

logic

for composite

generation. This signal determines

the

horizontal position

of

the

displayed

text.

Display Enable - This TTL

compatible

output

is

an

active high signal which indicates

the

CRTC

is

providing

addressing in

the

active 0 isplay Area.

REFRESH

MEMORY/CHARACTER

GENERATOR

ADDRESSING

The CRTC provides Memory Addresses (MAQ-MAI31

to

scan

the

Refresh RAM. Also provided are Raster

Addresses (RAO·RA41 for

the

character ROM.

Refresh Memory Addresses (MAO-MA131 - These 14

outputs

are used

to

refresh

the

CRT screen with pages

of

data located within a

16K

block

of

refresh memory. These

outputs

drive a TTL load and

30pF.

A high level on

MAO·MA13

is

a logical

"1."

Raster Addresses (RAO-RA4) - These 5

outputs

from

the internal Raster

Counter

address

the

Character

ROM

for the row

of

a

character.

These

outputs

drive a

TT

L load

and 3OpF. A high level (on RAO·RA4)

is

a logical

"1."

OTHER PINS

Cursor - This TTL

compatible

output

indicates Cursor

Display

to

external

Video

Processing Logic. Active high

signal.

Clock

(ClK)

-

The

ClK

TTL/MaS

compatible

input

is

used

to

synchronize all CRT

control

signals. An external

dot

counter

is

used

to

derive this signal which

is

usually

the

character rate

in

an alphanumeric CRT. The active

transition

is

high

to

low.

Light Pen

Strobe

(lPSTR

I - This high impedance

TTL/MOS

compatible

input

latches the current Refresh

Addresses

in

the

Register File. Latching

is

on

the low

to

high edge and

is

synchronized

internally

to

character clock.

VCC.

Gnd

RES - The RES

input

is

used

to

Reset

the

CRTC. An

input

low level

on

RES

forces CRTC

into

following

status:

(A) All the

counters

in

CRTC are cleared and

the

device stops

the

display operation.

(BI

All the

outputs

go

down

to

low level.

(C)

Control registers

in

CRTC are

not

affected and

remain unchanged.

This signal

is

different

from

other

M6800 family

in

the

following functions:

(AI RES signal

has

capability

of

reset function only

when

lPSTB

is

at

low level.

(B)

After

RES

has

gone

down

to

low level,

output

signals

of

MAO·MAI3

and

RAO·RA4,

synchronizing

with

ClK

low level, goes down

to

low level.

(At

least 1 cycle

ClK

signal

is

necessary for reset.)

(C)

The

C R TC

starts

the

0

isplay

operation

immediately

after

the

release

of

RES signal.

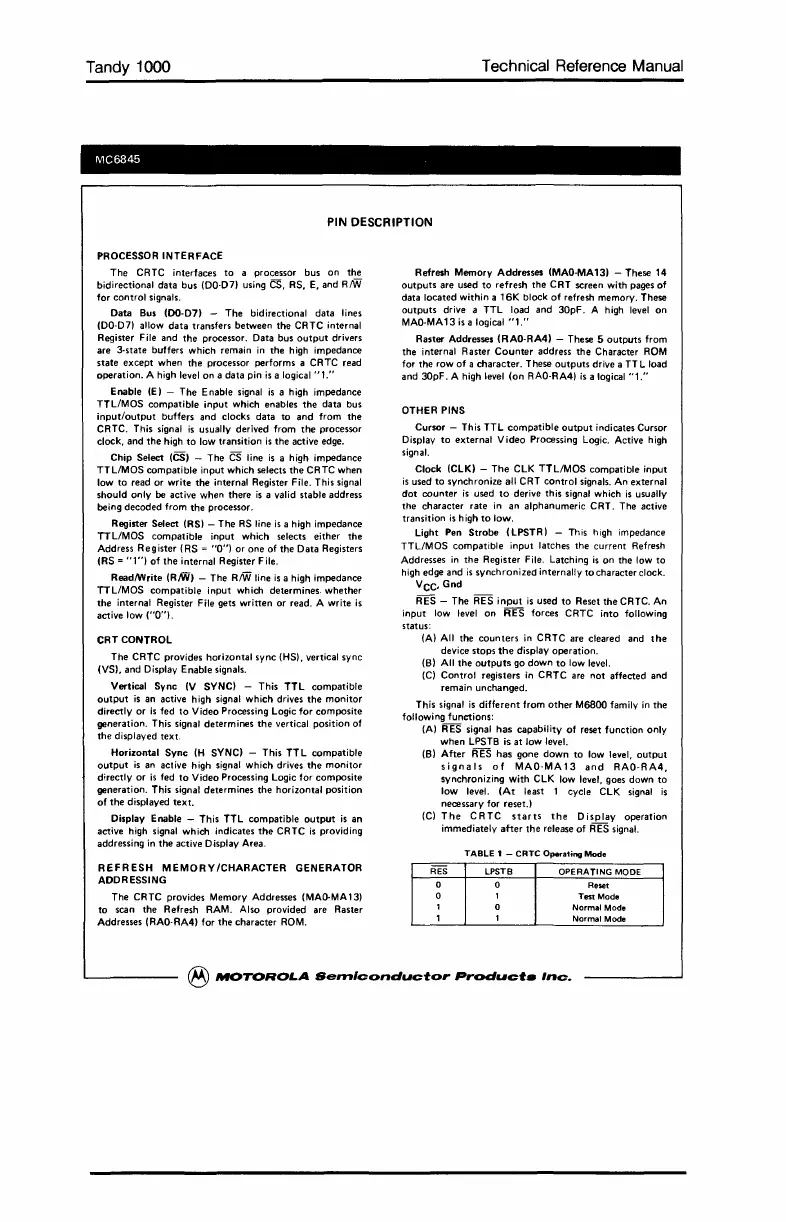

TABLE

1 - CRTC Operating

Mode

RES LPSTB

OPERATING

MODE

0

0

Reset

0

1

Test Mode

1

0

Normal Mode

1

1

Normal Mode

®

MOTOROLA

Senl'conductor

Product.

Inc.

Loading...

Loading...