92

83532002 Rev C

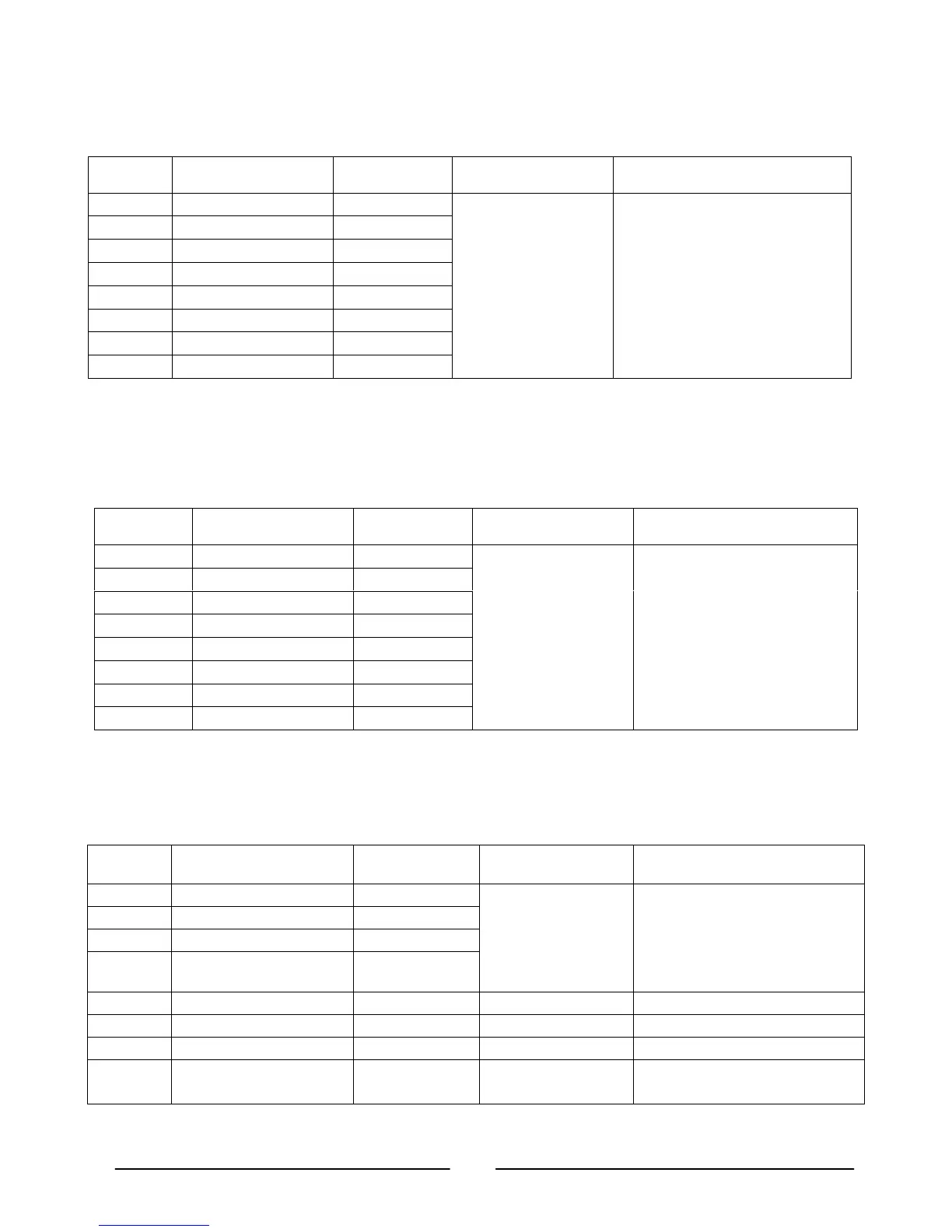

A. Fault Enable Register (FENA nn, FENA?)

The Fault Enable Register is set to the enable faults SRQs.

Table 8-12: Fault Enable Register

BIT

Enable

bit name

Fault symbol Bit Set condition Bit reset condition

0 (LSB) Spare bit SPARE

User command:

“FENA nn” where nn is

hexadecimal

User command: “FENA nn” where

nn is hexadecimal (if nn=”00”, no

fault SRQs will be generated).

1 AC Fail AC

2 Over Temperature OTP

3 Foldback FOLD

4 Over Voltage OVP

5 Shut Off SO

6 Output Off OFF

7(MSB) Enable ENA

B. Fault Event Register (FEVE?)

The Fault Event will set a bit if a condition occurs and it is enabled. The register is

cleared when FEVE?, CLS or RST commands are received.

Table 8-13: Fault Event Register

BIT

Enable

bit name

Fault symbol Bit Set condition Bit reset condition

0 (LSB) Spare bit SPARE Fault condition occurs

and it is enabled.

The fault can set a bit,

but when the fault

clears, the bit remains

set.

Entire Event Register is cleared

when user sends “FEVE?”

command to read the register.

“CLS” and power-up also clear

the Fault Event Register (the

Fault Event Register is not

cleared by RST).

1 AC Fail AC

2 Over Temperature OTP

3 Foldback FOLD

4 Over Voltage OVP

5 Shut Off SO

6 Output Off OFF

7(MSB) Enable ENA

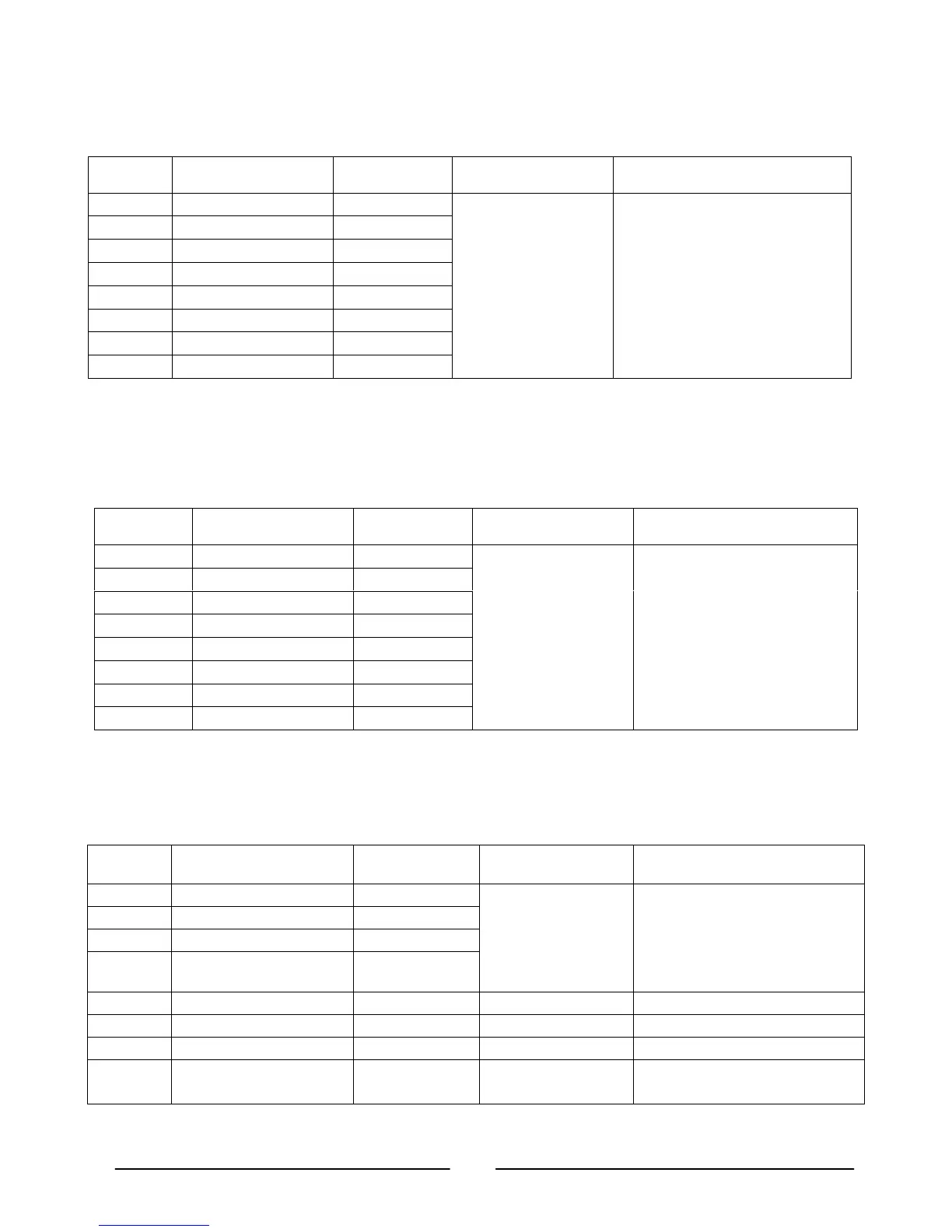

C. Status Enable Register (SENA nn, SENA?)

The Status Enable Register is set by the user to enable SRQs from changes in Power

Supply status.

Table 8-14: Status Enable Register

BIT Status name Status symbol Bit Set condition Bit reset condition

0 (LSB)

Constant Voltage

CV

User command:

“SENA nn” is

received, where nn is

hexadecimal bits.

User command: “SENA nn” is

received, where nn is

hexadecimal bits.

If “nn”=00, no SRQ is sent when

there is a change in Status

Condition Register.

1

Constant Current

CC

2

No Fault

NFLT

3

Fault active

FLT

4

Auto-Restart enabled

AST Always zero Always zero

5

Fold enabled

FDE Always zero Always zero

6

Spare

Spare Always zero Always zero

7 (MSB)

Local Mode

LCL

“SENA nn”

command

“SENA nn” command

Loading...

Loading...