ME310G1 Hardware Design Guide

1VV0301588 Rev. 16 Page 43 of 95 2021-10-27

5.7.3.1.Asynchronous Serial Port (USIF0)

The serial port 0 on the Telit ME310G1 module is a +1.8V UART with 5 RS232 signals.

It differs from the PC-RS232 in signal polarity (RS232 is reversed) and levels.

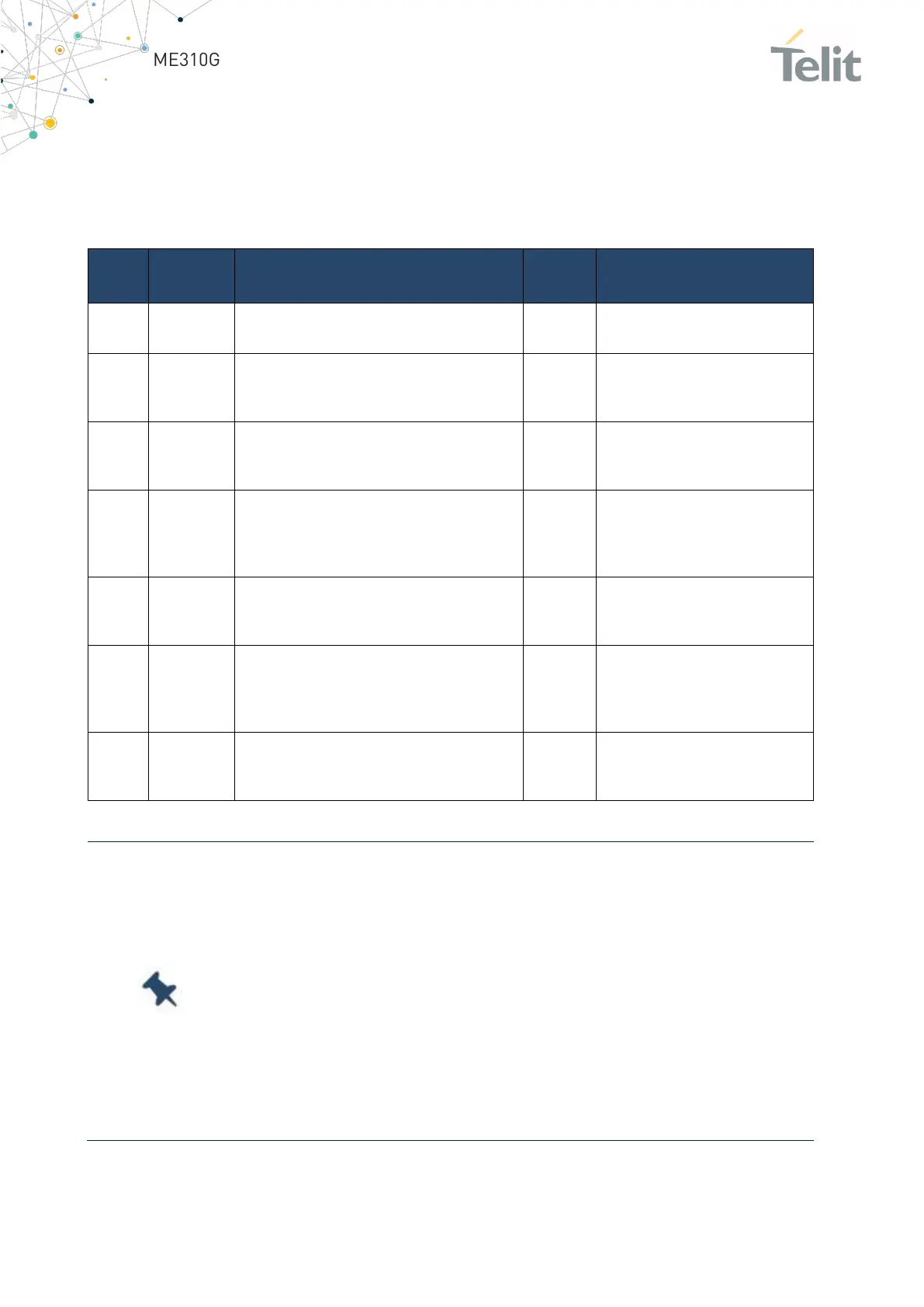

The following are the available signals:

Output transmit line of ME310G1

UART

Input receive of the

ME310G1 UART

Pull-up default during ON state

Input to the ME310G1 that

controls the DTE READY

condition

A3, A7, A9, A13, A17, B4, B6, B10, B12, B14,

B16, C19, D18, F8, F12, F18, G19, H6, H14,

J19, K18, M18, N19, P6, P14, T8, T12, U1, V2,

W19, Y2, Y4

Output from the ME310G1 that

controls the Hardware flow

control

Input to the ME310G1 that

controls the Hardware flow

control

Pull-up default during ON state

Output from the ME310G1 that

indicates the incoming call

condition

Table 29: Available signs * For alternate GPIO functions, refer to General Purpose I/O

Note: According to V.24, some signal names refer to the application

side, so on the ME310G1 side these signals are in the opposite

direction:

TXD on the application side is connected to the receiving line (here

named C103/TXD0)

RXD on the application side is connected to the transmit line (here

named C104/RXD0)

For reduced implementation, only the TXD, RXD lines can be

connected, the other lines can be left open.

Loading...

Loading...