AM3359, AM3358, AM3357, AM3356, AM3354, AM3352

SPRS717H –OCTOBER 2011–REVISED MAY 2015

www.ti.com

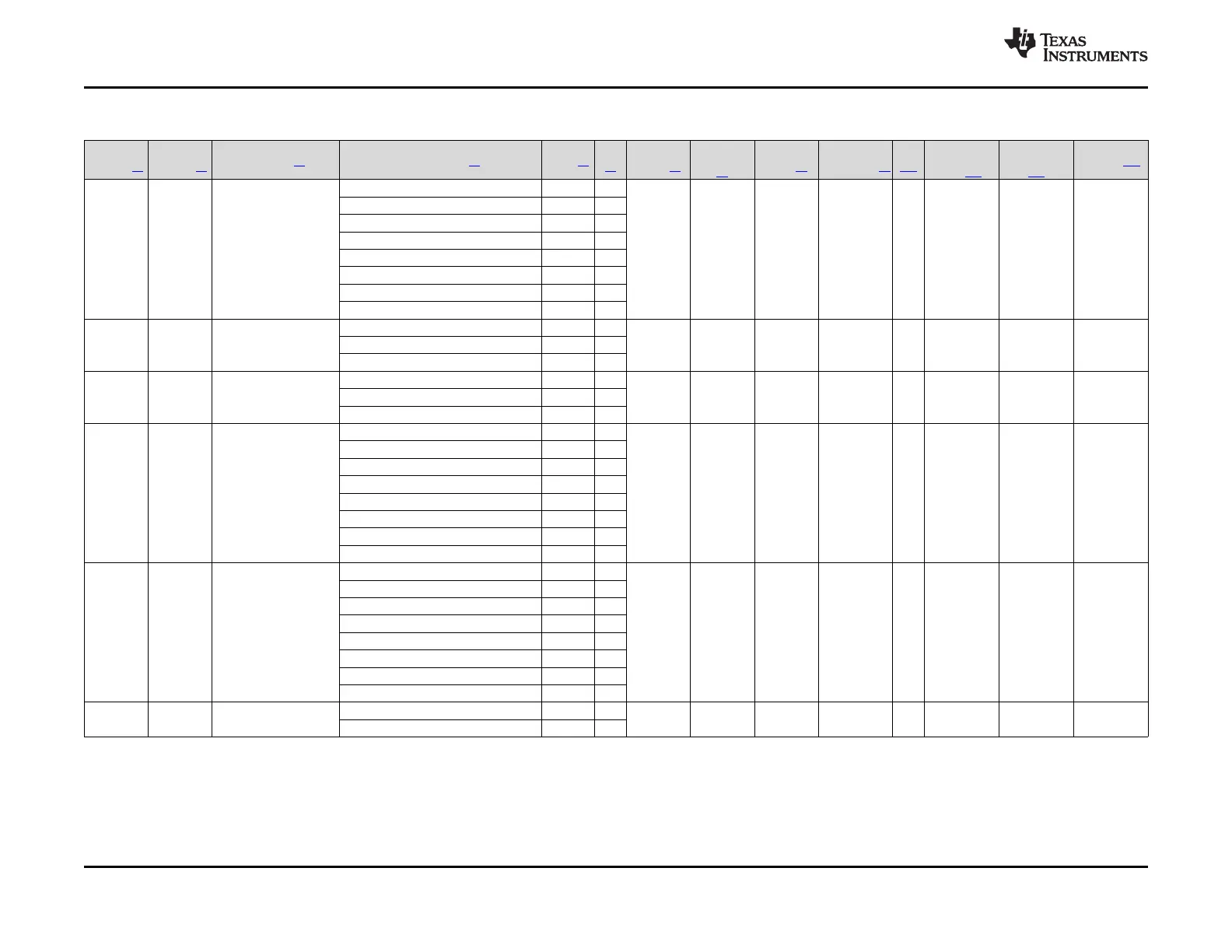

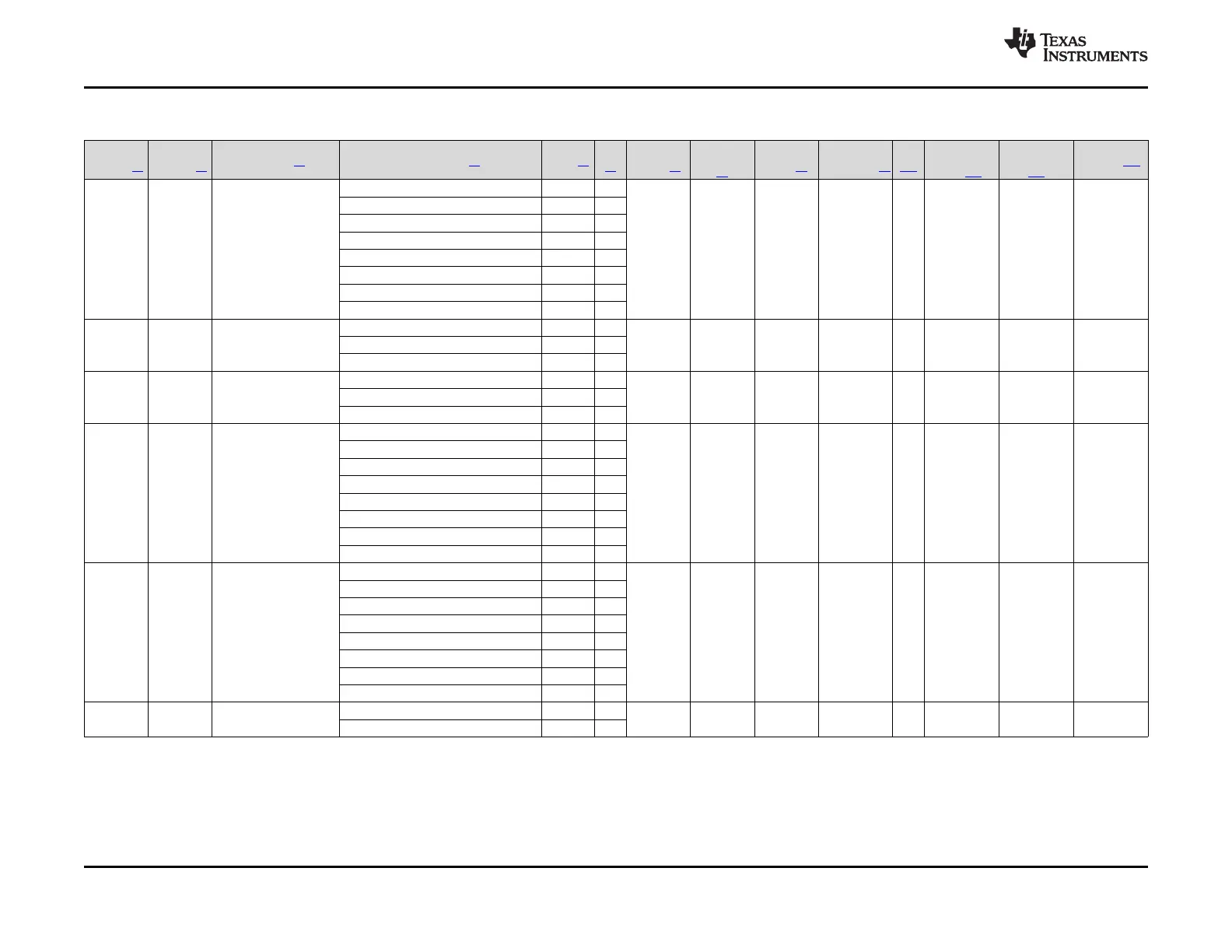

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

BALL RESET BUFFER PULLUP

ZCE BALL ZCZ BALL TYPE BALL RESET RESET REL. ZCE POWER / HYS

PIN NAME [2] SIGNAL NAME [3] MODE [4] REL. STATE STRENGTH /DOWN TYPE I/O CELL [13]

NUMBER [1] NUMBER [1] [5] STATE [6] MODE [8] ZCZ POWER [9] [10]

[7] (mA) [11] [12]

V17 U13 GPMC_AD15 gpmc_ad15 0 I/O L L 7 VDDSHV1 / Yes 6 PU/PD LVCMOS

VDDSHV2

lcd_data16 1 O

mmc1_dat7 2 I/O

mmc2_dat3 3 I/O

eQEP2_strobe 4 I/O

pr1_ecap0_ecap_capin_apwm_o 5 I/O

pr1_pru0_pru_r31_15 6 I

gpio1_15 7 I/O

V10 R7 GPMC_ADVn_ALE gpmc_advn_ale 0 O H H 7 VDDSHV1 / Yes 6 PU/PD LVCMOS

VDDSHV1

timer4 2 I/O

gpio2_2 7 I/O

V8 T6 GPMC_BEn0_CLE gpmc_be0n_cle 0 O H H 7 VDDSHV1 / Yes 6 PU/PD LVCMOS

VDDSHV1

timer5 2 I/O

gpio2_5 7 I/O

V18 U18 GPMC_BEn1 gpmc_be1n 0 O H H 7 VDDSHV1 / Yes 6 PU/PD LVCMOS

VDDSHV3

gmii2_col 1 I

gpmc_csn6 2 O

mmc2_dat3 3 I/O

gpmc_dir 4 O

pr1_mii1_rxlink 5 I

mcasp0_aclkr 6 I/O

gpio1_28 7 I/O

V16 V12 GPMC_CLK gpmc_clk 0 I/O L L 7 VDDSHV1 / Yes 6 PU/PD LVCMOS

VDDSHV2

lcd_memory_clk 1 O

gpmc_wait1 2 I

mmc2_clk 3 I/O

pr1_mii1_crs 4 I

pr1_mdio_mdclk 5 O

mcasp0_fsr 6 I/O

gpio2_1 7 I/O

W8 V6 GPMC_CSn0 gpmc_csn0 0 O H H 7 VDDSHV1 / Yes 6 PU/PD LVCMOS

VDDSHV1

gpio1_29 7 I/O

28 Terminal Configuration and Functions Copyright © 2011–2015, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352

Loading...

Loading...