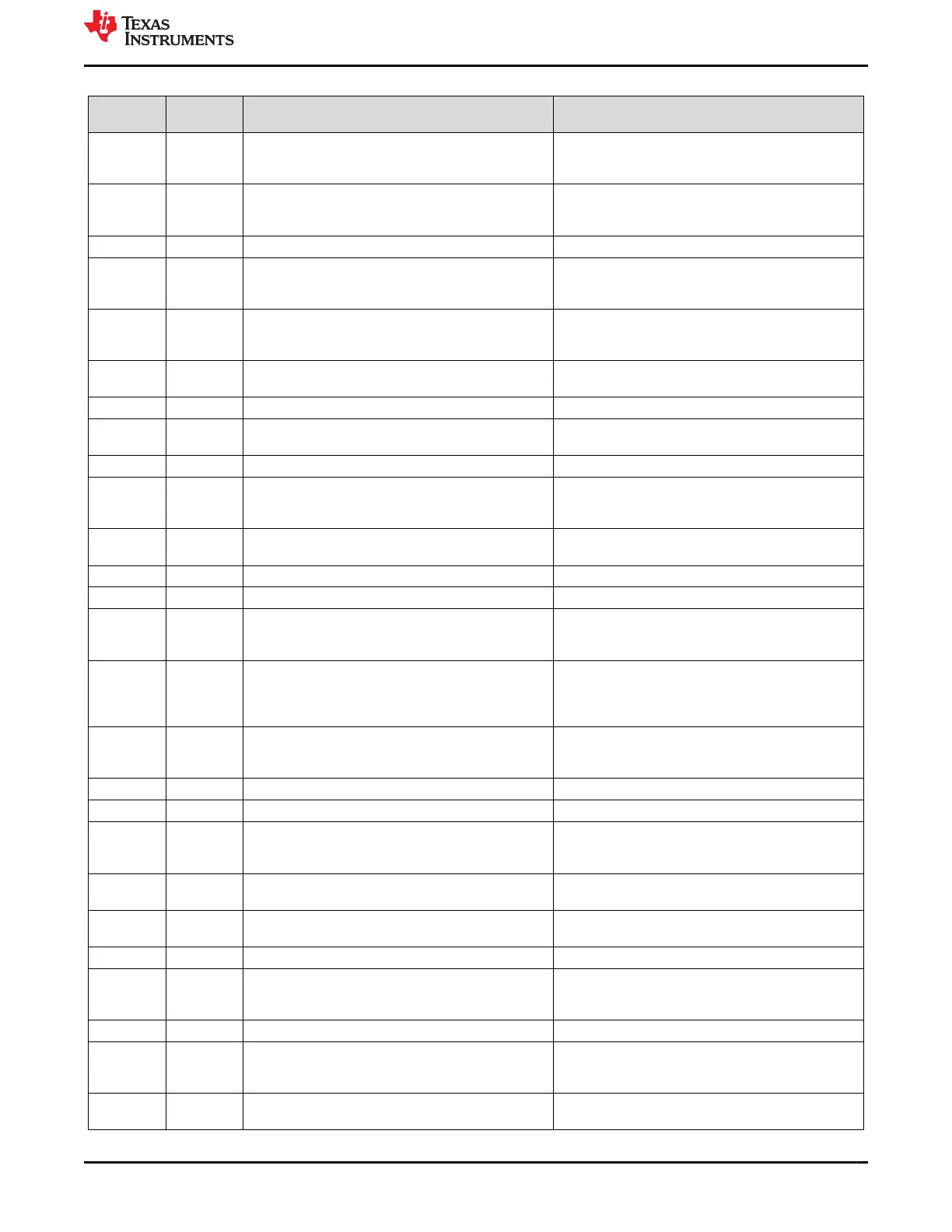

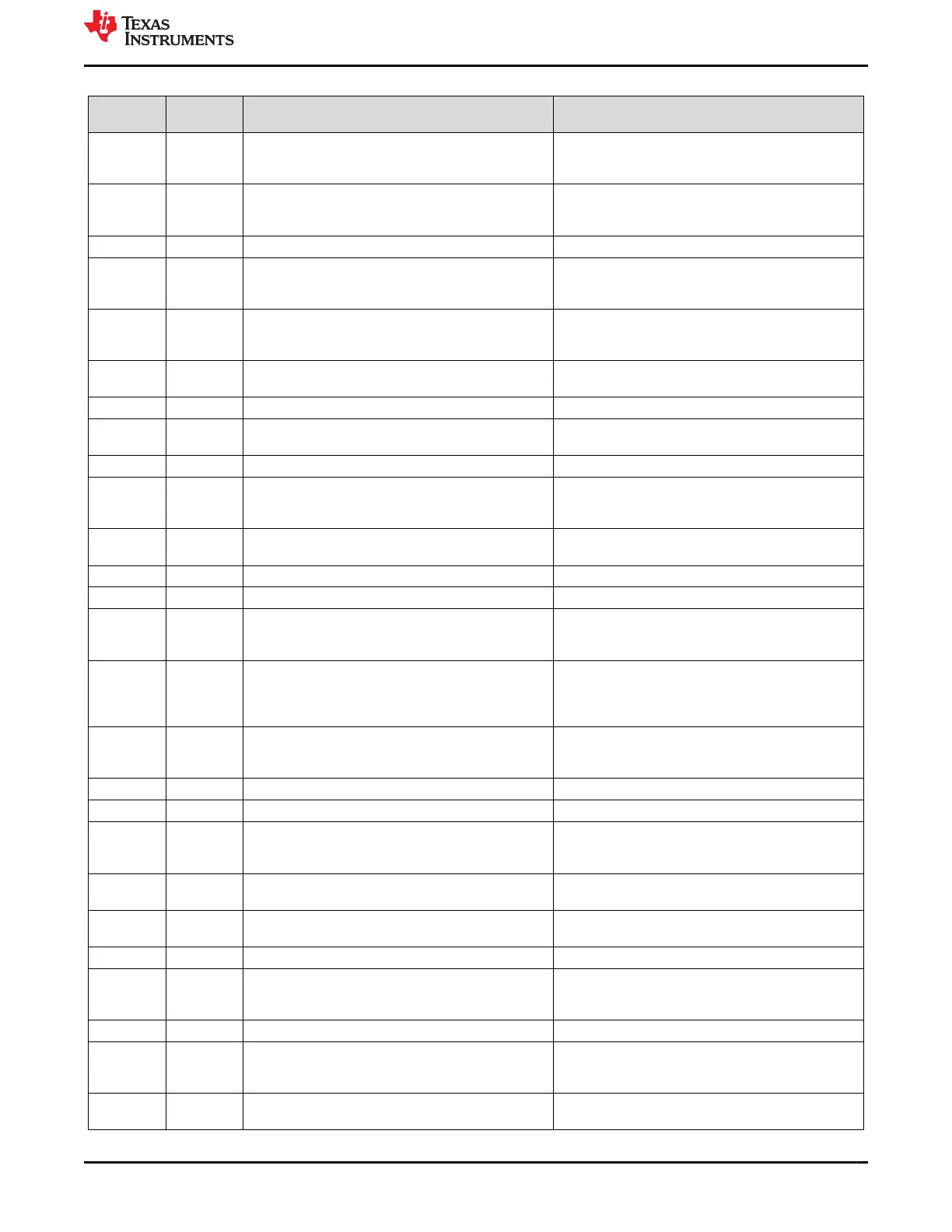

Table 3-24. Selection of PRG0 Signals on Application Connector (continued)

Connector

Pin SoC Ball Net Name Pin Multiplexed Signal Functions

D14 U21 GPMC0_AD1 FSI_RX2_D0, UART2_TXD, EHRPWM0_SYNCO,

TRC_CTL, GPIO0_16, PRG0_PWM2_TZ_OUT,

BOOTMODE01

D15 U18 GPMC0_AD4 FSI_RX3_D0, UART3_TXD, EHRPWM0_B,

TRC_DATA2, GPIO0_82, PRG0_PWM2_B0,

BOOTMODE04

D16 - DGND -

D17 V21 GPMC0_AD7 FSI_RX4_D1, UART4_TXD, EHRPWM_TZn_IN1,

EHRPWM8_A, TRC_DATA5, GPIO0_22,

PRG1_PWM2_A2, BOOTMODE07

D18 P19 GPMC0_CSN2 I2C2_SCL, TIMER_IO8, EQEP1_S,

EHRPWM_TZn_IN4, GPIO0_43,

PRG1_PWM2_TZ_IN

D19 R21 GPMC0_CSN3 I2C2_SDA, TIMER_IO9, EQEP1_I, GPMC0_A20,

EHRPWM_TZn_IN5, GPIO0_44

D20 - DGND -

D21 V18 GPMC0_AD13 FSI_RX1_D1, EHRPWM3_A, TRC_DATA11,

GPIO0_28, PRG0_PWM3_A0, BOOTMODE13

D22 - HSE_GPIO0_33 -

D23 W5 HSE_PRG0_PRU1_GPO7 PRG0_PRU1_GPI7, PRG0_IEP1_EDC_LATCH_IN1,

RGMII1_RD0, RMII1_RXD0, GPIO1_27, EQEP2_B,

UART4_TXD

D24 A17 HSE_MCAN0_TX/UART4_RXD TIMER_IO2, SYNC2_OUT, SPI4_CS1, GPIO1_60,

EQEP2_I, UART0_DTRn

D25 - DGND -

D26 - HSE_GPIO0_41 -

D27 P5 HSE_PRG0_PRU1_GPO18 PRG0_PRU1_GPI18, PRG0_IEP1_EDC_LATCH_IN0,

PRG0_PWM1_TZ_IN, MDIO0_MDIO, RMII1_TX_EN,

EHRPWM7_A, GPIO1_38, PRG0_ECAP0_SYNC_IN

D28 W6 HSE_PRG0_PRU0_GPO9 PRG0_PRU0_GPI9, PRG0_UART0_CTSn,

PRG0_PWM3_TZ_IN, RGMII1_RX_CTL,

RMII1_RX_ER, PRG0_IEP0_EDIO_DATA_IN_OUT28,

GPIO1_9, UART2_RXD

D29 C17 HSE_MCAN1_TX/I2C3_SCL ECAP1_IN_APWM_OUT, SYSCLKOUT0, TIMER_IO4,

UART5_RXD, EHRPWM_SOCA, GPIO1_62,

EQEP2_A, UART0_DCDn

D30 - DGND -

E16 - DGND -

E17 V20 GPMC0_AD6 FSI_RX4_D0, UART4_RXD, EHRPWM1_B,

TRC_DATA4, GPIO0_21, PRG0_PWM2_B1,

BOOTMODE06

E18 N17 GPMC0_DIR EQEP0_B, GPIO0_40, EHRPWM6_B,

PRG1_PWM2_B0

E19 R20 GPMC0_CSN1 EQEP0_I, EHRPWM_TZn_IN2, GPIO0_42,

EHRPWM6_SYNCO, PRG1_PWM2_TZ_OUT

E20 - DGND -

E21 W20 GPMC0_AD11 FSI_RX1_CLK, UART5_CTSn, EQEP1_A,

TRC_DATA9, GPIO0_26, EHRPWM7_A,

BOOTMODE11

E22 - DGND -

E23 Y5 HSE_PRG0_PRU1_GPO9 PRG0_PRU1_GPI9, PRG0_UART0_RXD,

RGMII1_RD1, PRG0_IEP0_EDIO_DATA_IN_OUT30,

GPIO1_29, EQEP0_I, UART5_RXD

E24 B17 HSE_MCAN0_RX/UART4_TXD UART4_TXD, TIMER_IO3, SYNC3_OUT, SPI4_CS2,

GPIO1_61, EQEP2_S, UART0_RIn

www.ti.com System Description

SPRUIX0C – FEBRUARY 2021 – REVISED JUNE 2021

Submit Document Feedback

AM64x/AM243x GP EVM User's Guide 51

Copyright © 2021 Texas Instruments Incorporated

Loading...

Loading...