www.ti.com

Enable and Reset

11

SNLU223–August 2017

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

DS90UB954-Q1EVM Quick Start

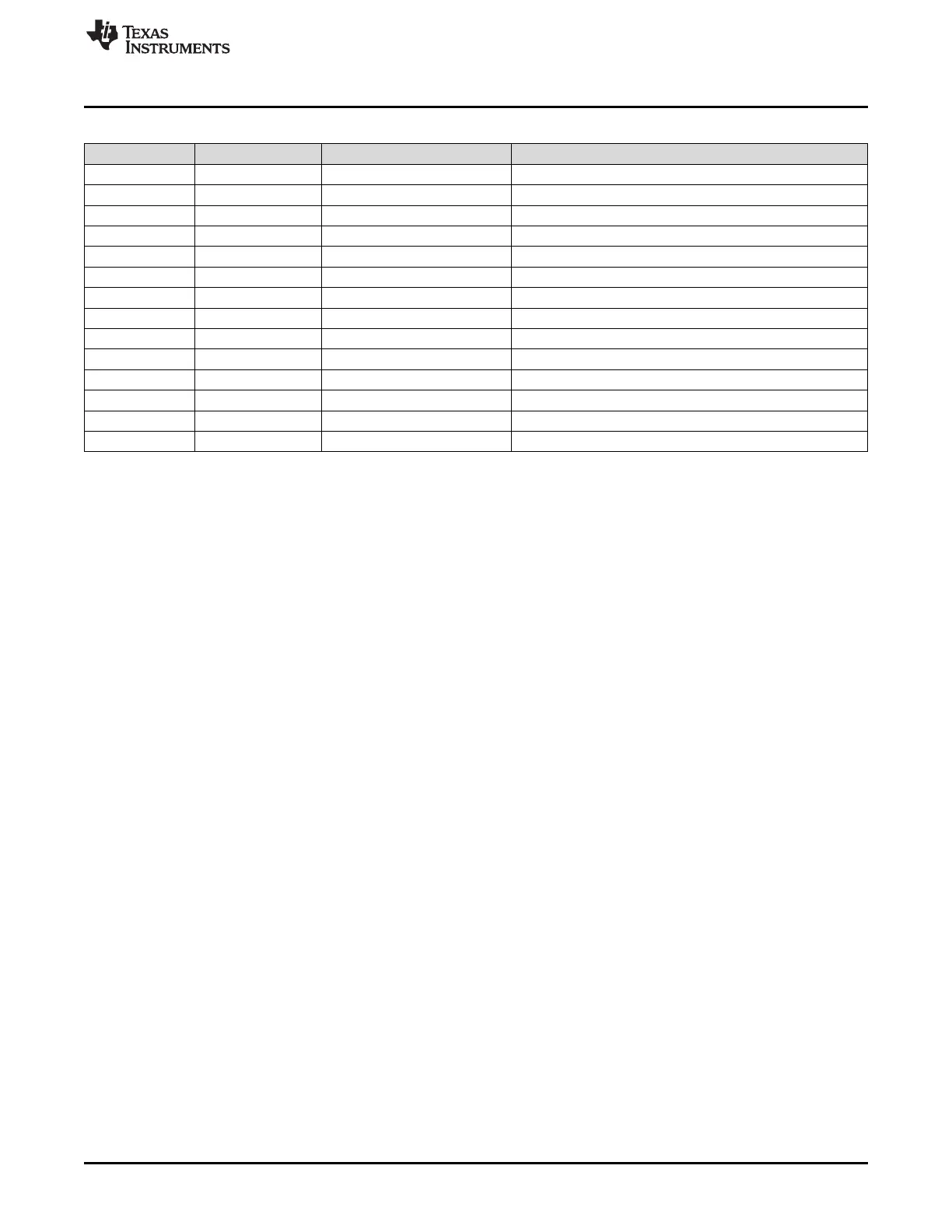

Table 12. LEDs

Reference LED Color LED Name Description

D3 Red VDDIO Illuminates on VDDIO Power

D4 Red VDD5V Illuminates on +5V

D5 Red VDD_EXT Illuminates if 12V Power is applied to DC-IN J24

D6 Orange VPOC_RX1 Illuminates if VPOC_RX1 is ON

D7 Orange VPOC_RX0 Illuminates if VPOC_RX0 is ON

D8 Orange PASS Illuminates if PASS pin is HIGH

D9 Green LOCK Illuminates if LOCK pin is HIGH

D10 Green GPIO6 Illuminates if GPIO6 is HIGH

D11 Green GPIO5 Illuminates if GPIO5 is HIGH

D12 Green GPIO4 Illuminates if GPIO48 is HIGH

D13 Green GPIO3/INTB Illuminates if GPIO3 is HIGH, or GPIO3 disabled (pulled-up)

D14 Green GPIO2 Illuminates if GPIO2 is HIGH

D15 Green GPIO1 Illuminates if GPIO1 is HIGH

D16 Green GPIO0 Illuminates if GPIO0 is HIGH

4 Enable and Reset

The DS90UB954-Q1 is enabled and reset by controlling the PDB input level. PDB has an internal pull

down, and should remain low until all supplies are stable. There are three device enable and reset/power-

down options for the EVM.

• RC timing option: The RC delay created with C123 and R131 connected to the PDB pin is the default

option for delaying PDB on the EVM. This is used for simplicity of debugging and using the device. TI

recommends using a GPIO signal from a host process or to drive PDB after all rails have settled in

customer designs.

• External control option: A momentary push-button switch, SW1, is available for manually driving the

PDB signal low while the button is held.

• Software control option: The PDB pin is also made available in the J24 and J26 CSI-2 output

connectors, allowing a host processor to control the PDB pin.

Loading...

Loading...