RM46L852

SPNS185 –SEPTEMBER 2012

www.ti.com

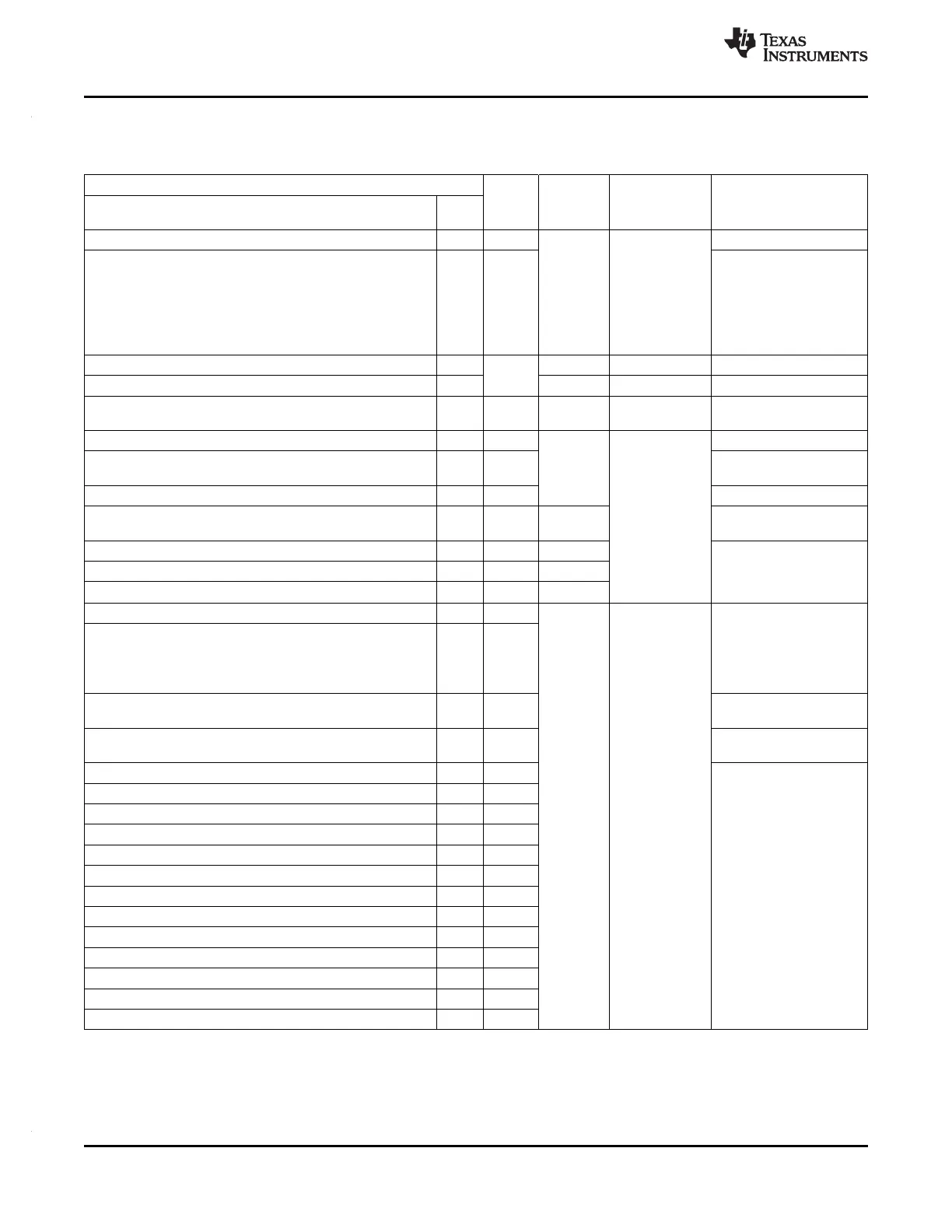

2.3.2.15 External Memory Interface (EMIF)

Table 2-42. External Memory Interface (EMIF)

Terminal Signal Default Pull Type Description

Type Pull State

Signal Name 337

ZWT

EMIF_CKE L3 Output Pull Down - EMIF Clock Enable

EMIF_CLK K3 I/O EMIF clock. This is an

output signal in functional

mode. It is gated off by

default, so that the signal

is tri-stated. PINMUX29[8]

must be cleared to enable

this output.

EMIF_nWE/EMIF_RNW D17 Output Pull Up - EMIF Read-Not-Write

EMIF_nOE E12 Pull Down - EMIF Read Enable

EMIF_nWAIT P3 I/O Pull Up Fixed, 20uA EMIF Extended Wait

Signal

EMIF_nWE/EMIF_RNW D17 Output Pull Up Programmable, EMIF Write Enable.

20uA

EMIF_nCAS R4 Output EMIF column address

strobe

EMIF_nRAS R3 Output EMIF row address strobe

EMIF_nCS[0]/N2HET2[7]

(1)

N17 Output Pull Down EMIF chip select,

synchronous

EMIF_nCS[2] L17 Output Pull Up EMIF chip selects,

asynchronous

EMIF_nCS[3]/N2HET2[9]

(1)

K17 Output Pull Down

This applies to chip

EMIF_nCS[4] M17 Output Pull Up

selects 2, 3 and 4

EMIF_nDQM[0] E10 Output Pull Down Programmable, EMIF Data Mask or Write

20uA Strobe.

EMIF_nDQM[1] E11 Output

Data mask for SDRAM

devices, write strobe for

connected asynchronous

devices.

EMIF_BA[0] E13 Output EMIF bank address or

address line

EMIF_BA[1]/N2HET2[5]

(1)

D16 Output EMIF bank address or

address line

EMIF_ADDR[0]/N2HET2[1]

(1)

D4 Output EMIF address

EMIF_ADDR[1]/N2HET2[3]

(1)

D5 Output

EMIF_ADDR[2] E6 Output

EMIF_ADDR[3] E7 Output

EMIF_ADDR[4] E8 Output

EMIF_ADDR[5] E9 Output

EMIF_ADDR[6]/NHET2[11]

(1)

C4 Output

EMIF_ADDR[7]/NHET2[13]

(1)

C5 Output

EMIF_ADDR[8]/NHET2[15]

(1)

C6 Output

EMIF_ADDR[9] C7 Output

EMIF_ADDR[10] C8 Output

EMIF_ADDR[11] C9 Output

EMIF_ADDR[12] C10 Output

(1) These signals are tri-stated and pulled down by default after power-up. Any application that requires the EMIF must set the bit 31 of the

system module general-purpose register GPREG1.

38 Device Package and Terminal Functions Copyright © 2012, Texas Instruments Incorporated

Submit Documentation Feedback

Loading...

Loading...