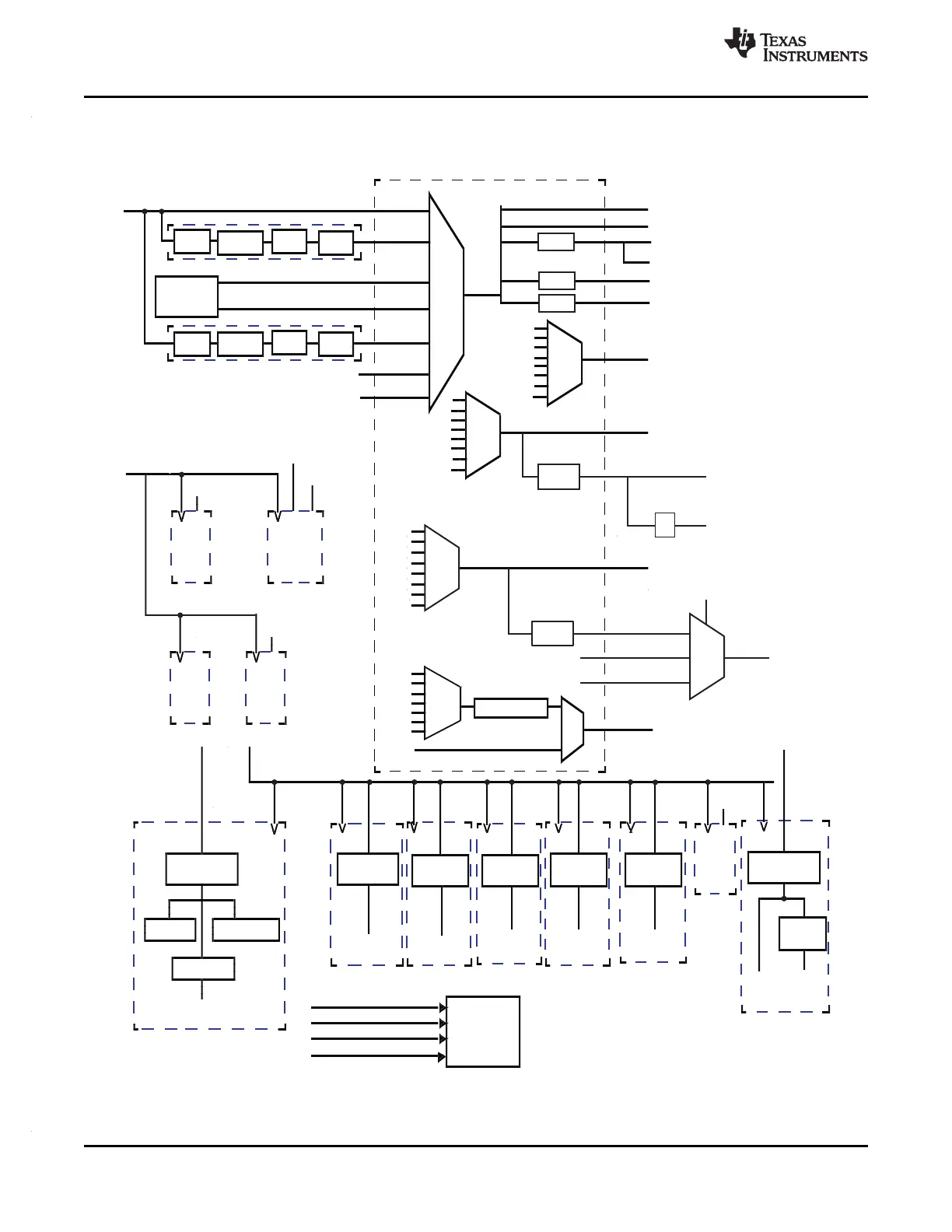

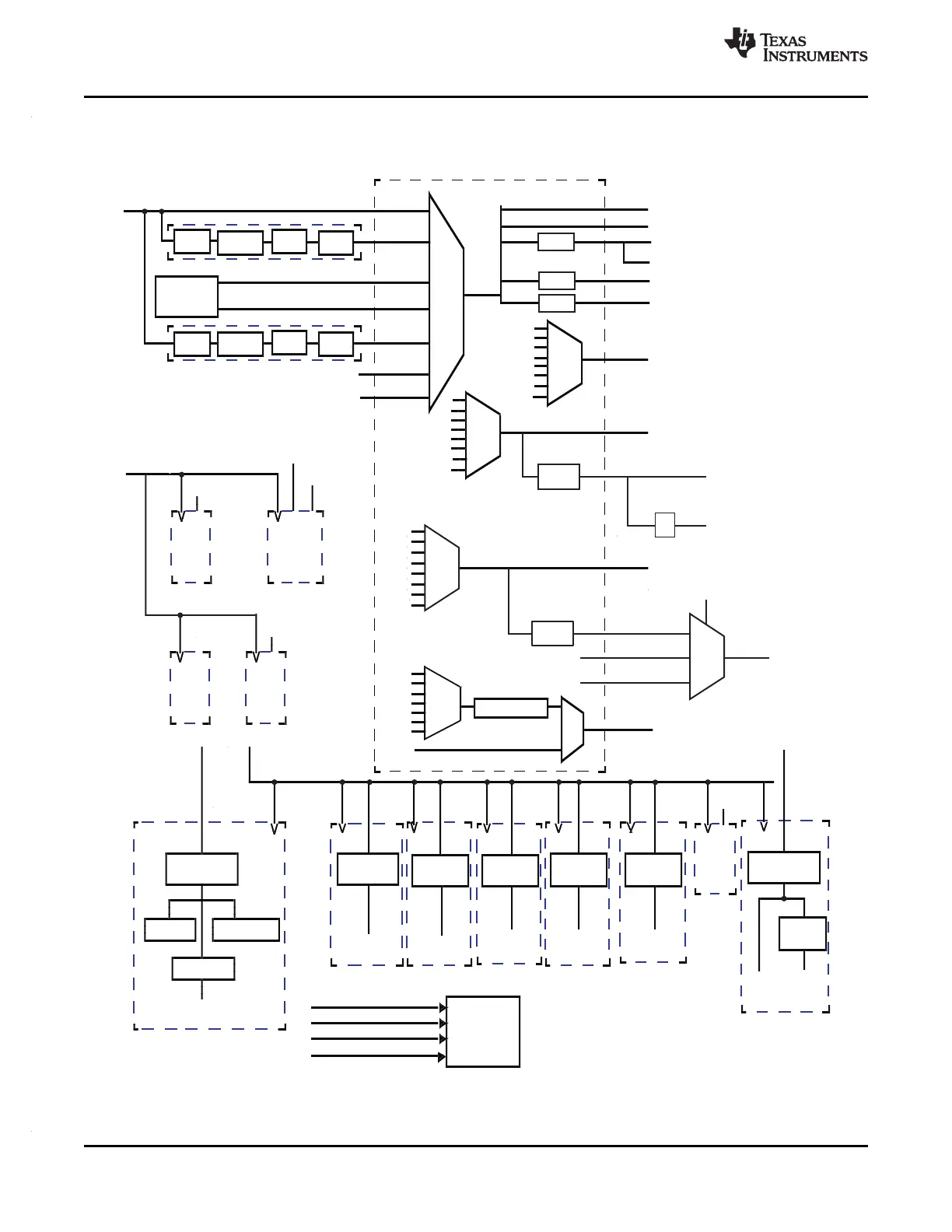

HCLK (toSYSTEM)

GCLK,GCLK2 (toCPU)

GCM

VCLK_peri (VCLK to peripherals onPCR1)

VCLK2(toN2HETx andHTUx)

/1..16

/1..16

OSCIN

LowPower

Oscillator

10MHz

80kHz

PLL #1(FMzPLL)

1

0

4

5

/1..64

X1..256

/1..8

/1..32

6

PLL #2

*

/1,2,..256

SPIx,MibSPIx

/2,3..2

24

LIN,SCI

SPI

LIN /SCI

/1,2..32

MibADCx

ADCLK

/1,2..65536

ExternalClock

ECLK

VCLK2

N2HETx

HRP

/1..64

LRP

/2

0

..2

5

Loop

ResolutionClock

High

BaudRate

BaudRate

VCLK2

Ethernet

VCLKA4_DIVR

/1..64 X1..256 /1..8

/1..32 *

EXTCLKIN1

EXTCLKIN2

3

7

VCLKA1(to DCANx)to

0

1

4

5

6

VCLK

3

7

RTICLK (toRTI,DWWD)

/1,2,4,or8

VCLK

0

1

4

5

6

3

7

VCLK3

VCLK3(toEthernet,USB)

/1..16

VCLK_sys (VCLK to systemmodules)

*thefrequencyatthisnodemustnot

exceedthemaximumHCLKspecifiation.

/1,2..256

I2C

I2Cbaud

rate

0

1

4

5

6

VCLK

3

7

NTU[1]

NTU[0]

NTU[2]

NTU[3]

RTI

PLL#2output

EXTCLKIN1

Reserved

Reserved

VCLK

/1,2,..1024

Phase_seg2

CANBaudRate

Phase_seg1

VCLKA1

Prop_seg

(FMzPLL)

VCLKA3_S(leftopen)

/DIVR

VCLKA3_DIVR

(toUSBDevice/48MHZ

andUSBHost/48MHz)

USBHost

VCLKA3_DIVR/4

VCLKA3_DIVR

DCANx

EMIF USBDevice

VCLKA3_DIVR

N2HETx

TU

VCLKA4_DIVR

/DIVR

PLL2ODCLK/8

PLL2ODCLK/16

VCLKA4_DIVR_EMAC

(toEMAC)

VCLKA4_S(leftopen)

0

1

4

5

6

VCLK

3

7

/4

VCLKA3_DIVR/4

(toUSBHost/12MHz)

VCLKA4_SRC

RM46L852

SPNS185 –SEPTEMBER 2012

www.ti.com

4.6.2.2 Mapping of Clock Domains to Device Modules

Each clock domain has a dedicated functionality as shown in the figures below.

Figure 4-7. Device Clock Domains

68 System Information and Electrical Specifications Copyright © 2012, Texas Instruments Incorporated

Submit Documentation Feedback

Loading...

Loading...