105

TMS320C6748

www.ti.com

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Peripheral Information and Electrical SpecificationsCopyright © 2009–2017, Texas Instruments Incorporated

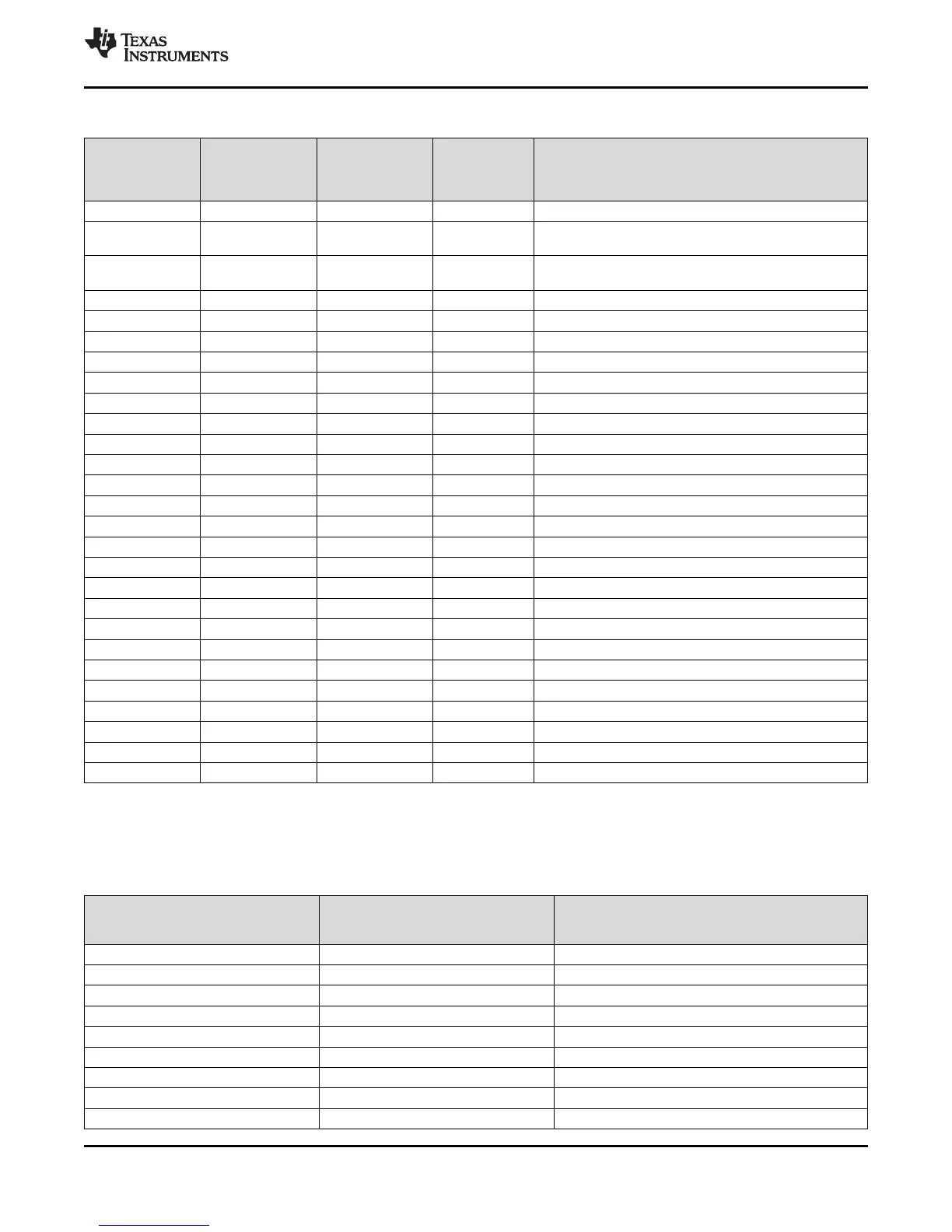

Table 6-14. EDMA3 Transfer Controller (EDMA3TC) Registers (continued)

EDMA3_0

Transfer

Controller 0

BYTE ADDRESS

EDMA3_0

Transfer

Controller 1

BYTE ADDRESS

EDMA3_1

Transfer

Controller 0

BYTE ADDRESS

ACRONYM REGISTER DESCRIPTION

0x01C0 8280 0x01C0 8680 0x01E3 8280 DFCNTRLD Destination FIFO Set Count Reload Register

0x01C0 8284 0x01C0 8684 0x01E3 8284 DFSRCBREF Destination FIFO Set Source Address B-Reference

Register

0x01C0 8288 0x01C0 8688 0x01E3 8288 DFDSTBREF Destination FIFO Set Destination Address B-Reference

Register

0x01C0 8300 0x01C0 8700 0x01E3 8300 DFOPT0 Destination FIFO Options Register 0

0x01C0 8304 0x01C0 8704 0x01E3 8304 DFSRC0 Destination FIFO Source Address Register 0

0x01C0 8308 0x01C0 8708 0x01E3 8308 DFCNT0 Destination FIFO Count Register 0

0x01C0 830C 0x01C0 870C 0x01E3 830C DFDST0 Destination FIFO Destination Address Register 0

0x01C0 8310 0x01C0 8710 0x01E3 8310 DFBIDX0 Destination FIFO B-Index Register 0

0x01C0 8314 0x01C0 8714 0x01E3 8314 DFMPPRXY0 Destination FIFO Memory Protection Proxy Register 0

0x01C0 8340 0x01C0 8740 0x01E3 8340 DFOPT1 Destination FIFO Options Register 1

0x01C0 8344 0x01C0 8744 0x01E3 8344 DFSRC1 Destination FIFO Source Address Register 1

0x01C0 8348 0x01C0 8748 0x01E3 8348 DFCNT1 Destination FIFO Count Register 1

0x01C0 834C 0x01C0 874C 0x01E3 834C DFDST1 Destination FIFO Destination Address Register 1

0x01C0 8350 0x01C0 8750 0x01E3 8350 DFBIDX1 Destination FIFO B-Index Register 1

0x01C0 8354 0x01C0 8754 0x01E3 8354 DFMPPRXY1 Destination FIFO Memory Protection Proxy Register 1

0x01C0 8380 0x01C0 8780 0x01E3 8380 DFOPT2 Destination FIFO Options Register 2

0x01C0 8384 0x01C0 8784 0x01E3 8384 DFSRC2 Destination FIFO Source Address Register 2

0x01C0 8388 0x01C0 8788 0x01E3 8388 DFCNT2 Destination FIFO Count Register 2

0x01C0 838C 0x01C0 878C 0x01E3 838C DFDST2 Destination FIFO Destination Address Register 2

0x01C0 8390 0x01C0 8790 0x01E3 8390 DFBIDX2 Destination FIFO B-Index Register 2

0x01C0 8394 0x01C0 8794 0x01E3 8394 DFMPPRXY2 Destination FIFO Memory Protection Proxy Register 2

0x01C0 83C0 0x01C0 87C0 0x01E3 83C0 DFOPT3 Destination FIFO Options Register 3

0x01C0 83C4 0x01C0 87C4 0x01E3 83C4 DFSRC3 Destination FIFO Source Address Register 3

0x01C0 83C8 0x01C0 87C8 0x01E3 83C8 DFCNT3 Destination FIFO Count Register 3

0x01C0 83CC 0x01C0 87CC 0x01E3 83CC DFDST3 Destination FIFO Destination Address Register 3

0x01C0 83D0 0x01C0 87D0 0x01E3 83D0 DFBIDX3 Destination FIFO B-Index Register 3

0x01C0 83D4 0x01C0 87D4 0x01E3 83D4 DFMPPRXY3 Destination FIFO Memory Protection Proxy Register 3

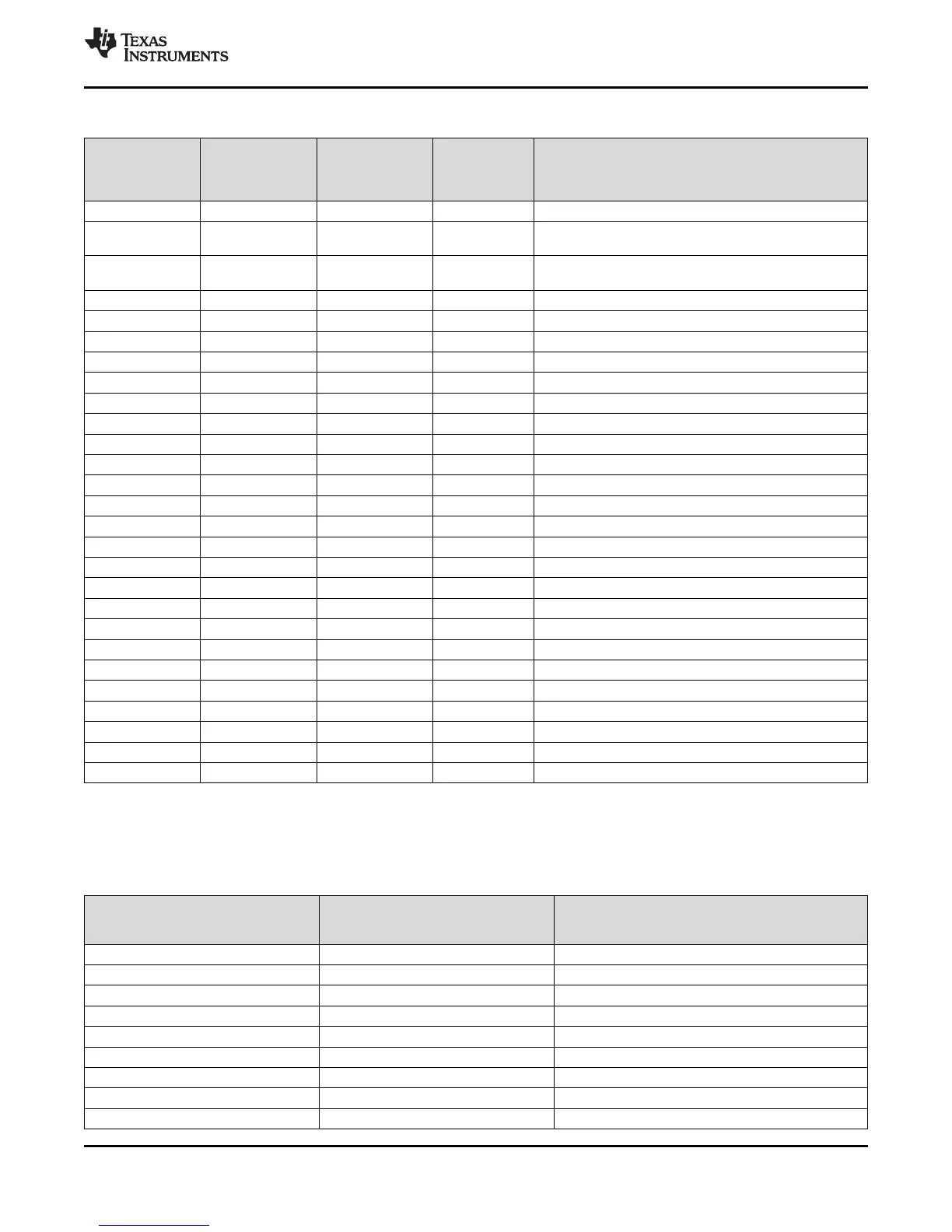

Table 6-15 shows an abbreviation of the set of registers which make up the parameter set for each of 128

EDMA3 events. Each of the parameter register sets consist of 8 32-bit word entries. Table 6-16 shows the

parameter set entry registers with relative memory address locations within each of the parameter sets.

Table 6-15. EDMA3 Parameter Set RAM

EDMA3_0

Channel Controller 0

BYTE ADDRESS RANGE

EDMA3_1

Channel Controller 0

BYTE ADDRESS RANGE

DESCRIPTION

0x01C0 4000 - 0x01C0 401F 0x01E3 4000 - 0x01E3 401F Parameters Set 0 (8 32-bit words)

0x01C0 4020 - 0x01C0 403F 0x01E3 4020 - 0x01E3 403F Parameters Set 1 (8 32-bit words)

0x01C0 4040 - 0x01CC0 405F 0x01E3 4040 - 0x01CE3 405F Parameters Set 2 (8 32-bit words)

0x01C0 4060 - 0x01C0 407F 0x01E3 4060 - 0x01E3 407F Parameters Set 3 (8 32-bit words)

0x01C0 4080 - 0x01C0 409F 0x01E3 4080 - 0x01E3 409F Parameters Set 4 (8 32-bit words)

0x01C0 40A0 - 0x01C0 40BF 0x01E3 40A0 - 0x01E3 40BF Parameters Set 5 (8 32-bit words)

... ... ...

0x01C0 4FC0 - 0x01C0 4FDF 0x01E3 4FC0 - 0x01E3 4FDF Parameters Set 126 (8 32-bit words)

0x01C0 4FE0 - 0x01C0 4FFF 0x01E3 4FE0 - 0x01E3 4FFF Parameters Set 127 (8 32-bit words)

Loading...

Loading...