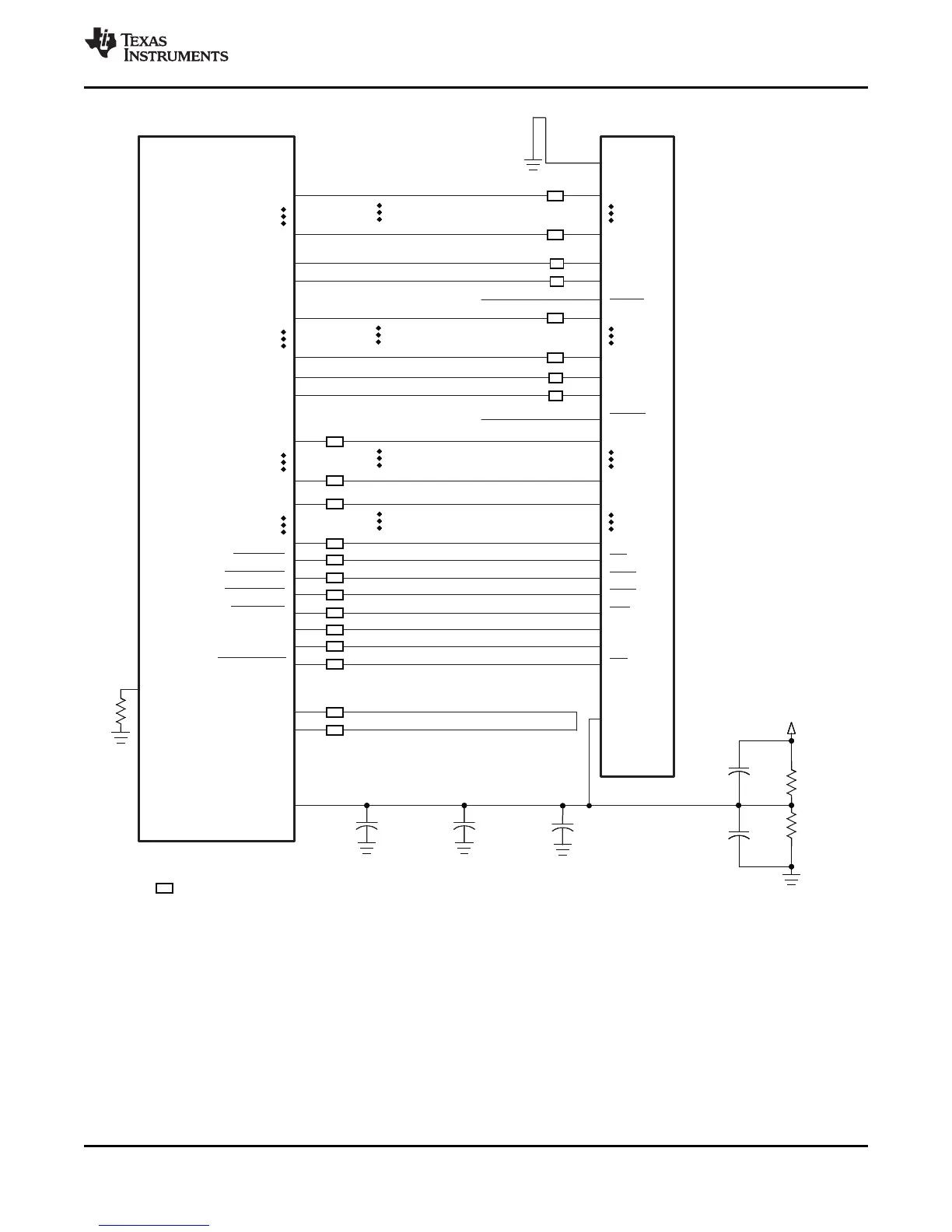

DDR2/mDDR Memory Controller

DDR_D[7]

DDR2/mDDR

DDR_DQM[0]

ODT

DQ0

DQ7

DDR_D[8]

DDR_D[15]

DQ8

DQ15

LDM

LDQS

LDQS

DDR_DQM[1]

DDR_DQS[1]

UDM

UDQS

UDQS

DDR_BA[0]

DDR_BA[2]

BA0

BA2

DDR_A[0]

DDR_A[13]

A0

DDR_CS

DDR_CAS

CS

CAS

DDR_RAS

DDR_WE

RAS

WE

DDR_CKE

CKE

DDR_CLKP

DDR_CLKN

CK

CK

DDR_DQGATE0

DDR_DQGATE1

DDR_ZP

DDR_VREF

1 K Ω 1%

DDR_DVDD18

VREF

1 K Ω 1%

0.1 μF

0.1 μF

0.1 Fμ

(2)

0.1 Fμ

(2)

50 5Ω %

T

Terminator, if desired. See terminator comments.

DQ7

A13

0.1 μF

0.1 μF

T

Terminator, if desired. See terminator comments.

DDR_D[0]

NC

TTT

TTT

TTT

TTT

TTT

TTT

TTT

TTT

TTT

TTT

TTT

TTT

TTT

TTT

TTT

TTT

TTT

TTT

TTT

T

T

T

T

T

T

VREF

(3)

T

Terminator, if desired. See terminator comments.

0.1 Fμ

(2)

DDR_DQS[0]

NC

(1)

121

TMS320C6748

www.ti.com

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Peripheral Information and Electrical SpecificationsCopyright © 2009–2017, Texas Instruments Incorporated

(1) See Figure 6-25 for DQGATE routing specifications.

(2) For DDR2, one of these capacitors can be eliminated if the divider and its capacitors are placed near a device VREF pin. For mDDR,

these capacitors can be eliminated completely.

(3) VREF applies in the case of DDR2 memories. For mDDR, the DDR_VREF pin still needs to be connected to the divider circuit.

Figure 6-18. DDR2/mDDR Single-Memory High Level Schematic

Loading...

Loading...