144

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

www.ti.com

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Peripheral Information and Electrical Specifications Copyright © 2009–2017, Texas Instruments Incorporated

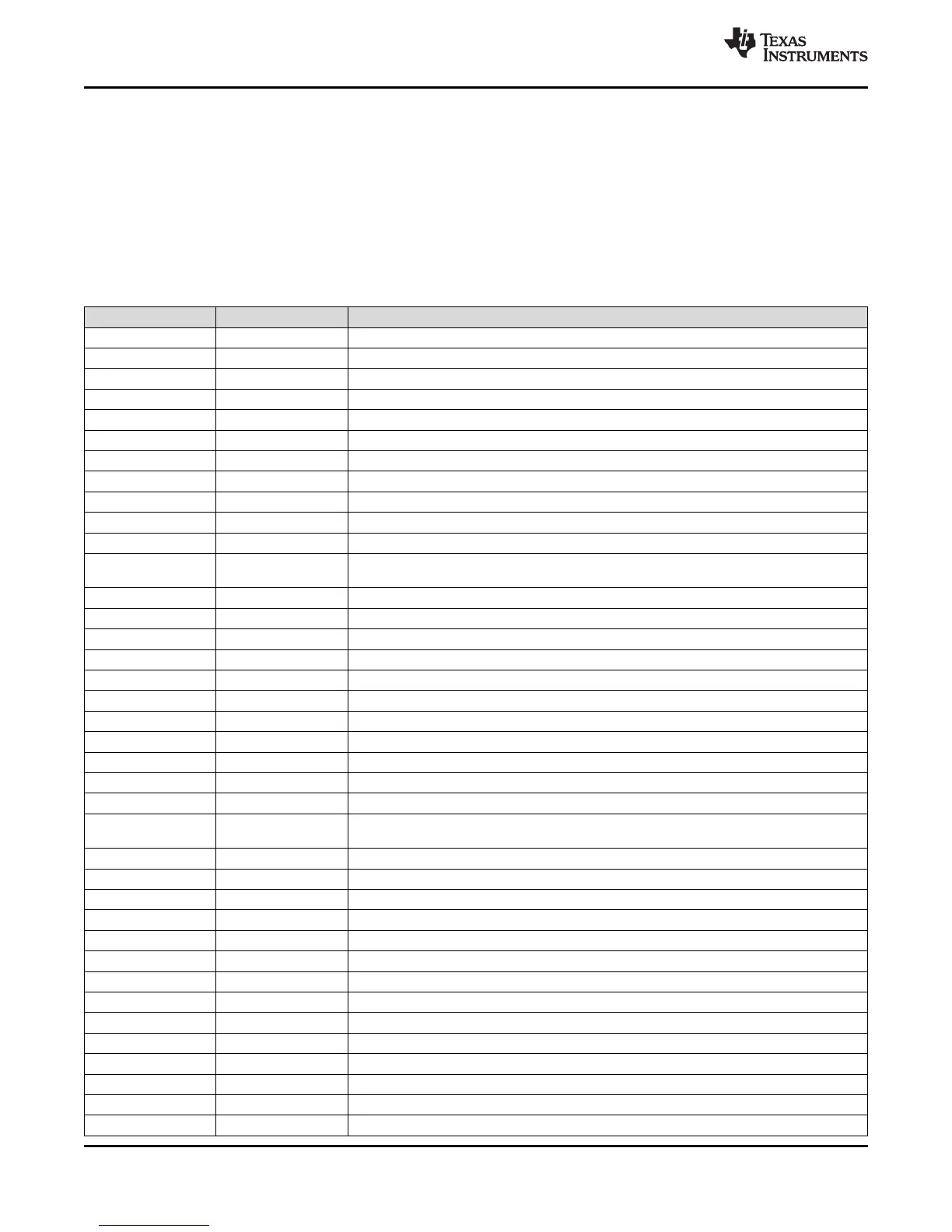

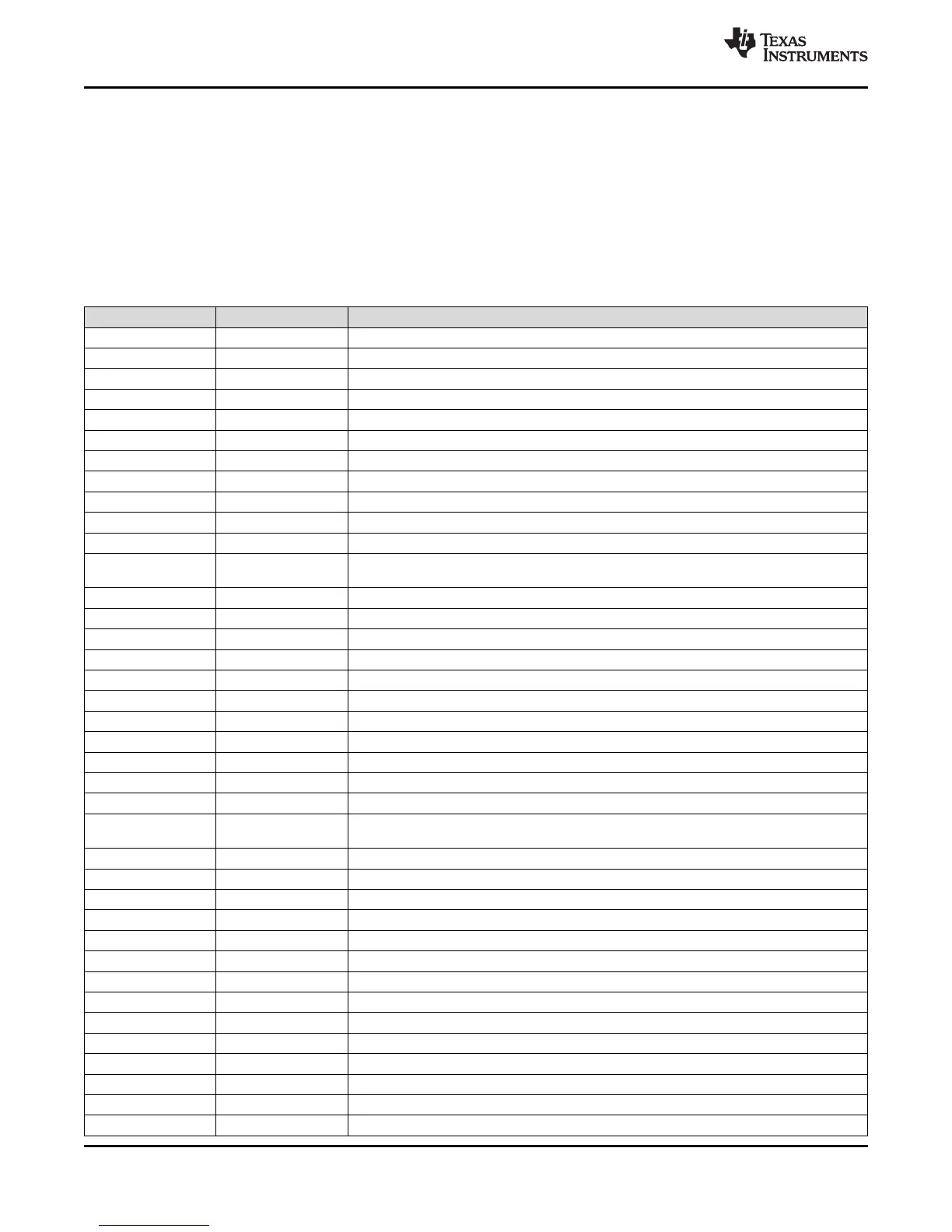

6.15.1 McASP Peripheral Registers Description(s)

Registers for the McASP are summarized in Table 6-49. The registers are accessed through the

peripheral configuration port. The receive buffer registers (RBUF) and transmit buffer registers (XBUF) can

also be accessed through the DMA port, as listed in Table 6-50

Registers for the McASP Audio FIFO (AFIFO) are summarized in Table 6-51. Note that the AFIFO Write

FIFO (WFIFO) and Read FIFO (RFIFO) have independent control and status registers. The AFIFO control

registers are accessed through the peripheral configuration port.

Table 6-49. McASP Registers Accessed Through Peripheral Configuration Port

BYTE ADDRESS ACRONYM REGISTER DESCRIPTION

0x01D0 0000 REV Revision identification register

0x01D0 0010 PFUNC Pin function register

0x01D0 0014 PDIR Pin direction register

0x01D0 0018 PDOUT Pin data output register

0x01D0 001C PDIN Read returns: Pin data input register

0x01D0 001C PDSET Writes affect: Pin data set register (alternate write address: PDOUT)

0x01D0 0020 PDCLR Pin data clear register (alternate write address: PDOUT)

0x01D0 0044 GBLCTL Global control register

0x01D0 0048 AMUTE Audio mute control register

0x01D0 004C DLBCTL Digital loopback control register

0x01D0 0050 DITCTL DIT mode control register

0x01D0 0060

RGBLCTL

Receiver global control register: Alias of GBLCTL, only receive bits are affected - allows

receiver to be reset independently from transmitter

0x01D0 0064 RMASK Receive format unit bit mask register

0x01D0 0068 RFMT Receive bit stream format register

0x01D0 006C AFSRCTL Receive frame sync control register

0x01D0 0070 ACLKRCTL Receive clock control register

0x01D0 0074 AHCLKRCTL Receive high-frequency clock control register

0x01D0 0078 RTDM Receive TDM time slot 0-31 register

0x01D0 007C RINTCTL Receiver interrupt control register

0x01D0 0080 RSTAT Receiver status register

0x01D0 0084 RSLOT Current receive TDM time slot register

0x01D0 0088 RCLKCHK Receive clock check control register

0x01D0 008C REVTCTL Receiver DMA event control register

0x01D0 00A0

XGBLCTL

Transmitter global control register. Alias of GBLCTL, only transmit bits are affected - allows

transmitter to be reset independently from receiver

0x01D0 00A4 XMASK Transmit format unit bit mask register

0x01D0 00A8 XFMT Transmit bit stream format register

0x01D0 00AC AFSXCTL Transmit frame sync control register

0x01D0 00B0 ACLKXCTL Transmit clock control register

0x01D0 00B4 AHCLKXCTL Transmit high-frequency clock control register

0x01D0 00B8 XTDM Transmit TDM time slot 0-31 register

0x01D0 00BC XINTCTL Transmitter interrupt control register

0x01D0 00C0 XSTAT Transmitter status register

0x01D0 00C4 XSLOT Current transmit TDM time slot register

0x01D0 00C8 XCLKCHK Transmit clock check control register

0x01D0 00CC XEVTCTL Transmitter DMA event control register

0x01D0 0100 DITCSRA0 Left (even TDM time slot) channel status register (DIT mode) 0

0x01D0 0104 DITCSRA1 Left (even TDM time slot) channel status register (DIT mode) 1

0x01D0 0108 DITCSRA2 Left (even TDM time slot) channel status register (DIT mode) 2

Loading...

Loading...