Copyright © 2009–2017, Texas Instruments IncorporatedPeripheral Information and Electrical Specifications

Submit Documentation Feedback

Product Folder Links: TMS320C6748

166

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

www.ti.com

(1) These parameters are in addition to the general timings for SPI master modes (Table 6-68).

(2) P = SYSCLK2 period; M = t

c(SPC)M

(SPI master bit clock period)

(3) Figure shows only Polarity = 0, Phase = 0 as an example. Table gives parameters for all four master clocking modes.

(4) In the case where the master SPI is ready with new data before SPI0_ENA assertion.

(5) In the case where the master SPI is ready with new data before SPI0_EN A deassertion.

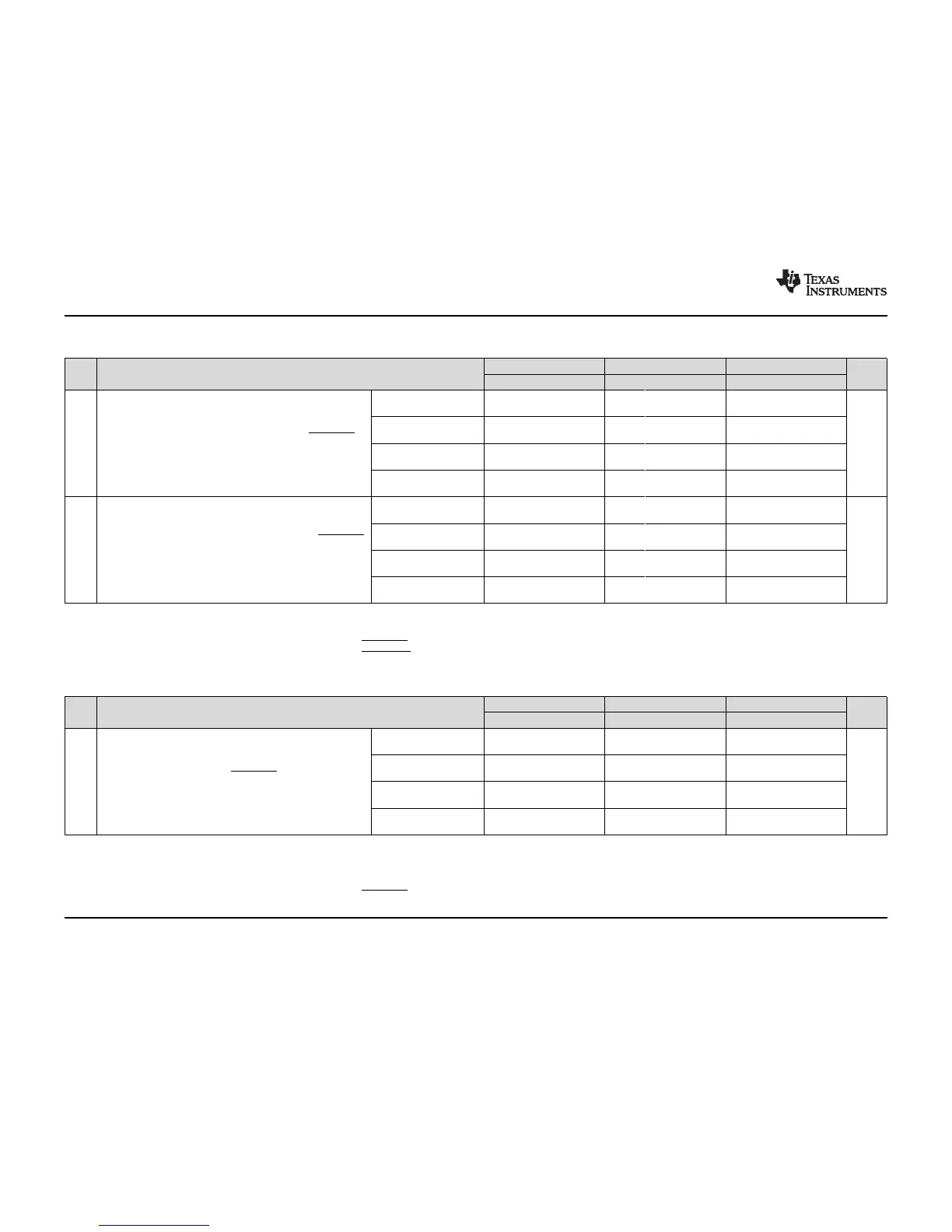

Table 6-70. Additional SPI0 Master Timings, 4-Pin Enable Option

(1)(2)(3)

NO. PARAMETER

1.3V, 1.2V 1.1V 1.0V

UNIT

MIN MAX MIN MAX MIN MAX

17 t

d(ENA_SPC)M

Delay from slave assertion of SPI0_ENA

active to first SPI0_CLK from master.

(4)

Polarity = 0, Phase = 0,

to SPI0_CLK rising

3P+5 3P+5 3P+6

ns

Polarity = 0, Phase = 1,

to SPI0_CLK rising

0.5M+3P+5 0.5M+3P+5 0.5M+3P+6

Polarity = 1, Phase = 0,

to SPI0_CLK falling

3P+5 3P+5 3P+6

Polarity = 1, Phase = 1,

to SPI0_CLK falling

0.5M+3P+5 0.5M+3P+5 0.5M+3P+6

18 t

d(SPC_ENA)M

Max delay for slave to deassert SPI0_ENA

after final SPI0_CLK edge to ensure

master does not begin the next transfer.

(5)

Polarity = 0, Phase = 0,

from SPI0_CLK falling

0.5M+P+5 0.5M+P+5 0.5M+P+6

ns

Polarity = 0, Phase = 1,

from SPI0_CLK falling

P+5 P+5 P+6

Polarity = 1, Phase = 0,

from SPI0_CLK rising

0.5M+P+5 0.5M+P+5 0.5M+P+6

Polarity = 1, Phase = 1,

from SPI0_CLK rising

P+5 P+5 P+6

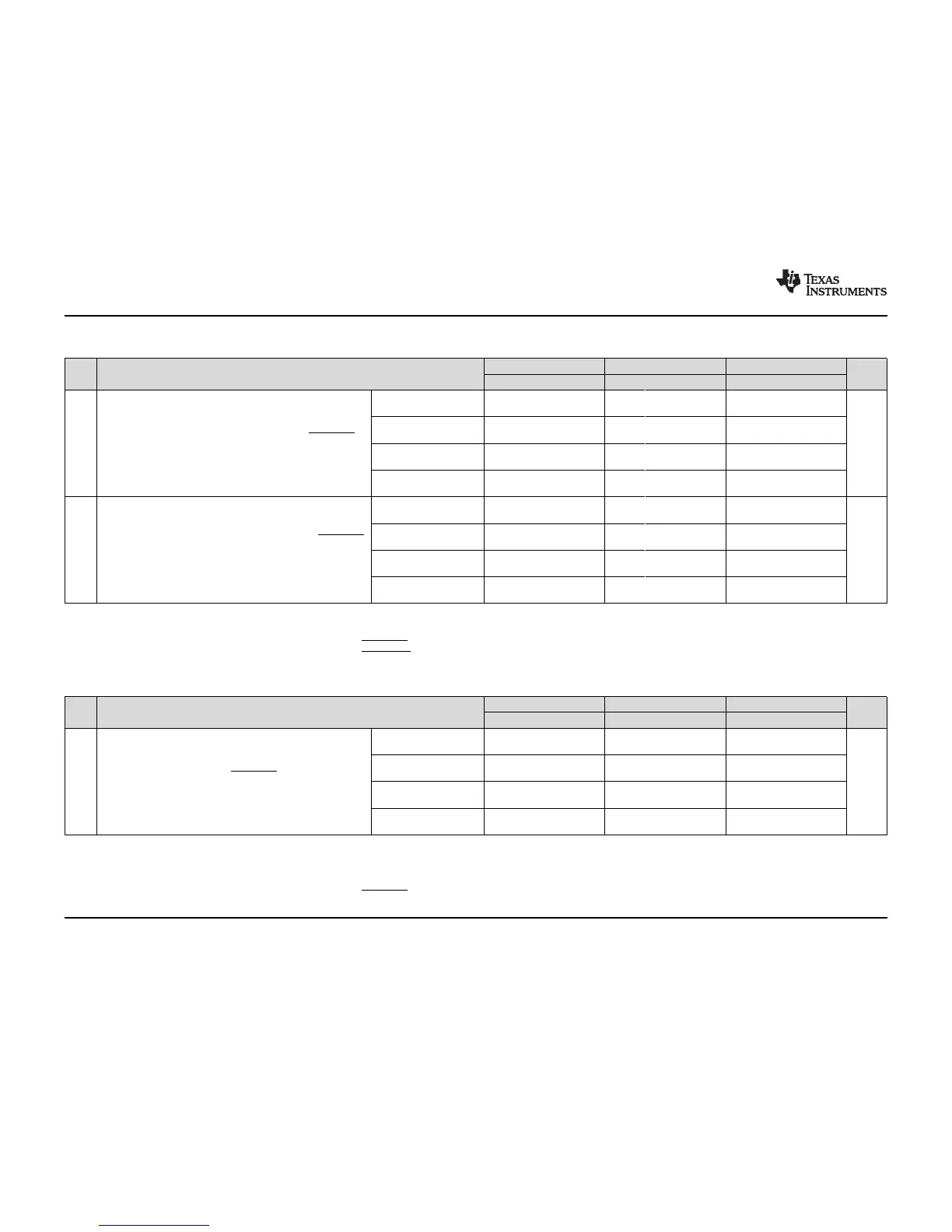

(1) These parameters are in addition to the general timings for SPI master modes (Table 6-68).

(2) P = SYSCLK2 period; M = t

c(SPC)M

(SPI master bit clock period)

(3) Figure shows only Polarity = 0, Phase = 0 as an example. Table gives parameters for all four master clocking modes.

(4) In the case where the master SPI is ready with new data before SPI0_SCS assertion.

(5) This delay can be increased under software control by the register bit field SPIDELAY.C2TDELAY[4:0].

Table 6-71. Additional SPI0 Master Timings, 4-Pin Chip Select Option

(1)(2)(3)

NO. PARAMETER

1.3V, 1.2V 1.1V 1.0V

UNIT

MIN MAX MIN MAX MIN MAX

19 t

d(SCS_SPC)M

Delay from SPI0_SCS active to first

SPI0_CLK

(4) (5)

Polarity = 0, Phase = 0,

to SPI0_CLK rising

2P-1 2P-2 2P-3

ns

Polarity = 0, Phase = 1,

to SPI0_CLK rising

0.5M+2P-1 0.5M+2P-2 0.5M+2P-3

Polarity = 1, Phase = 0,

to SPI0_CLK falling

2P-1 2P-2 2P-3

Polarity = 1, Phase = 1,

to SPI0_CLK falling

0.5M+2P-1 0.5M+2P-2 0.5M+2P-3

Loading...

Loading...