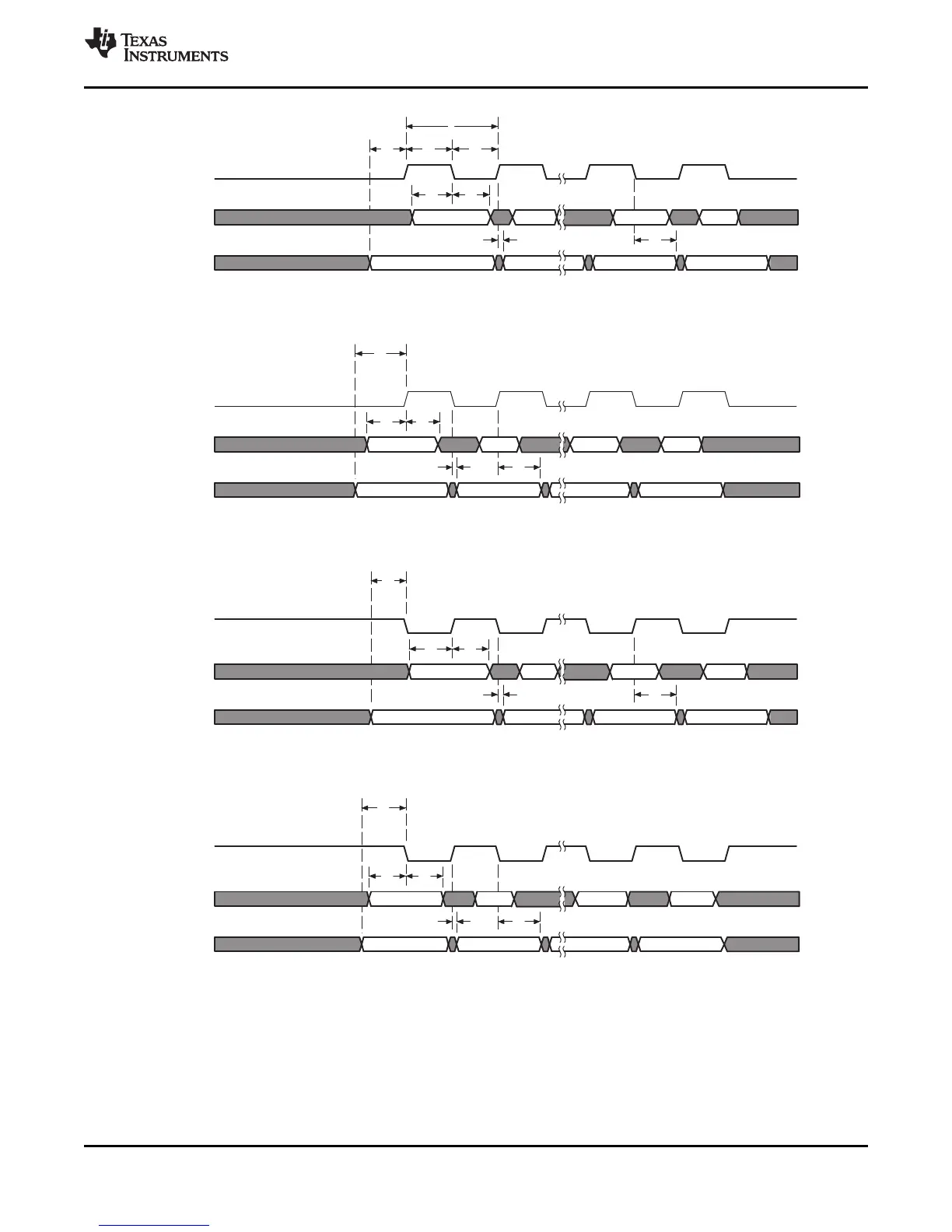

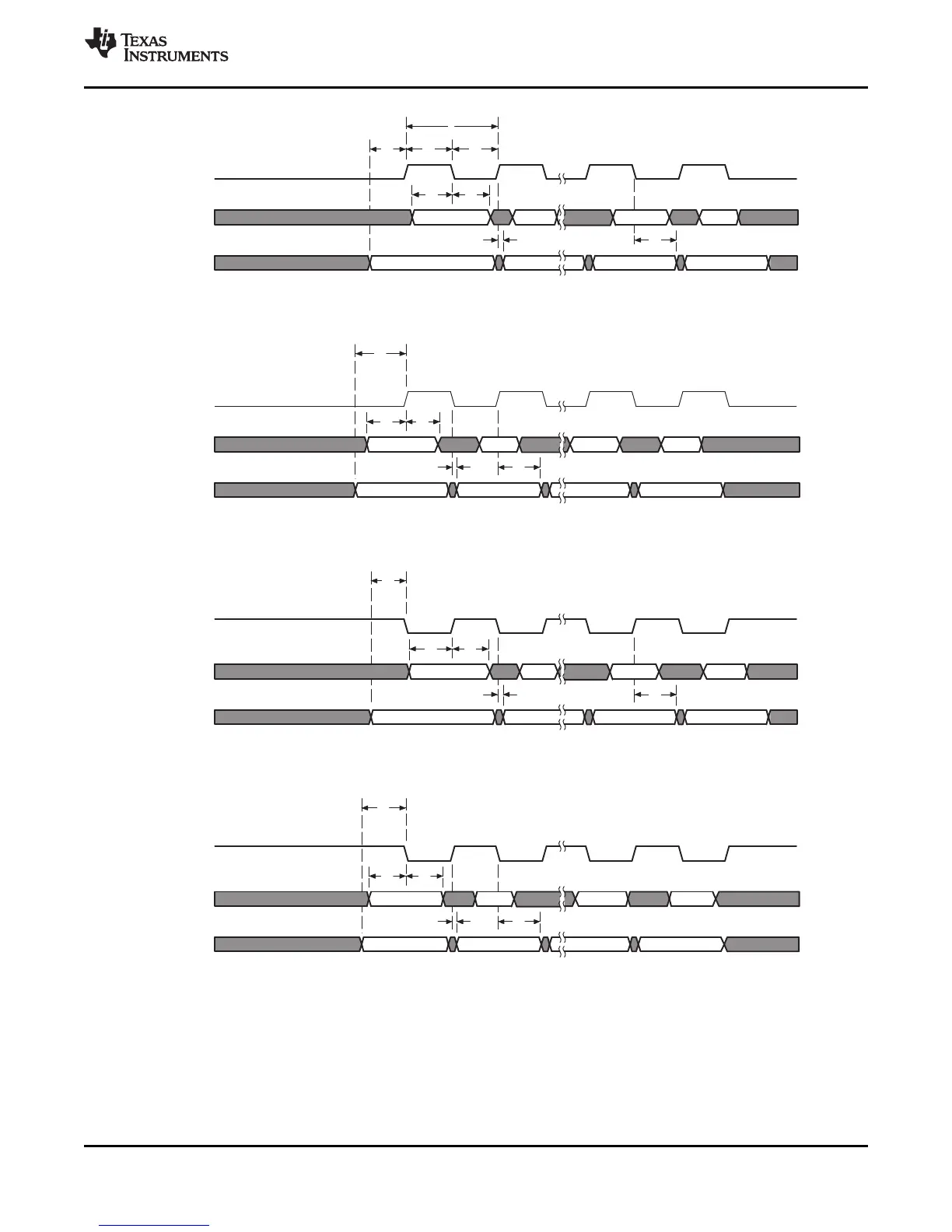

SPIx_CLK

SPIx_SIMO

SPIx_SOMI

SPIx_CLK

SPIx_SIMO

SPIx_SOMI

SPIx_CLK

SPIx_SIMO

SPIx_SOMI

SPIx_CLK

SPIx_SIMO

SPIx_SOMI

SI(0) SI(1) SI(n−1) SI(n)

SO(0) SO(1) SO(n−1) SO(n)

SI(0) SI(1) SI(n−1) SI(n)

SO(0) SO(1) SO(n−1) SO(n)

SI(0) SI(1) SI(n−1) SI(n)

SO(0) SO(1) SO(n−1) SO(n)

SI(0) SI(1) SI(n−1) SI(n)

SO(0) SO(1) SO(n−1) SO(n)

14

14

15

15

15

15

16

16

16

16

1110

14

9

12

12

12

12

13

13

13

13

14

SLAVE MODE

POLARITY = 0 PHASE = 0

SLAVE MODE

POLARITY = 0 PHASE = 1

SLAVE MODE

POLARITY = 1 PHASE = 0

SLAVE MODE

POLARITY = 1 PHASE = 1

179

TMS320C6748

www.ti.com

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Peripheral Information and Electrical SpecificationsCopyright © 2009–2017, Texas Instruments Incorporated

Figure 6-39. SPI Timings—Slave Mode

Loading...

Loading...