193

TMS320C6748

www.ti.com

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Peripheral Information and Electrical SpecificationsCopyright © 2009–2017, Texas Instruments Incorporated

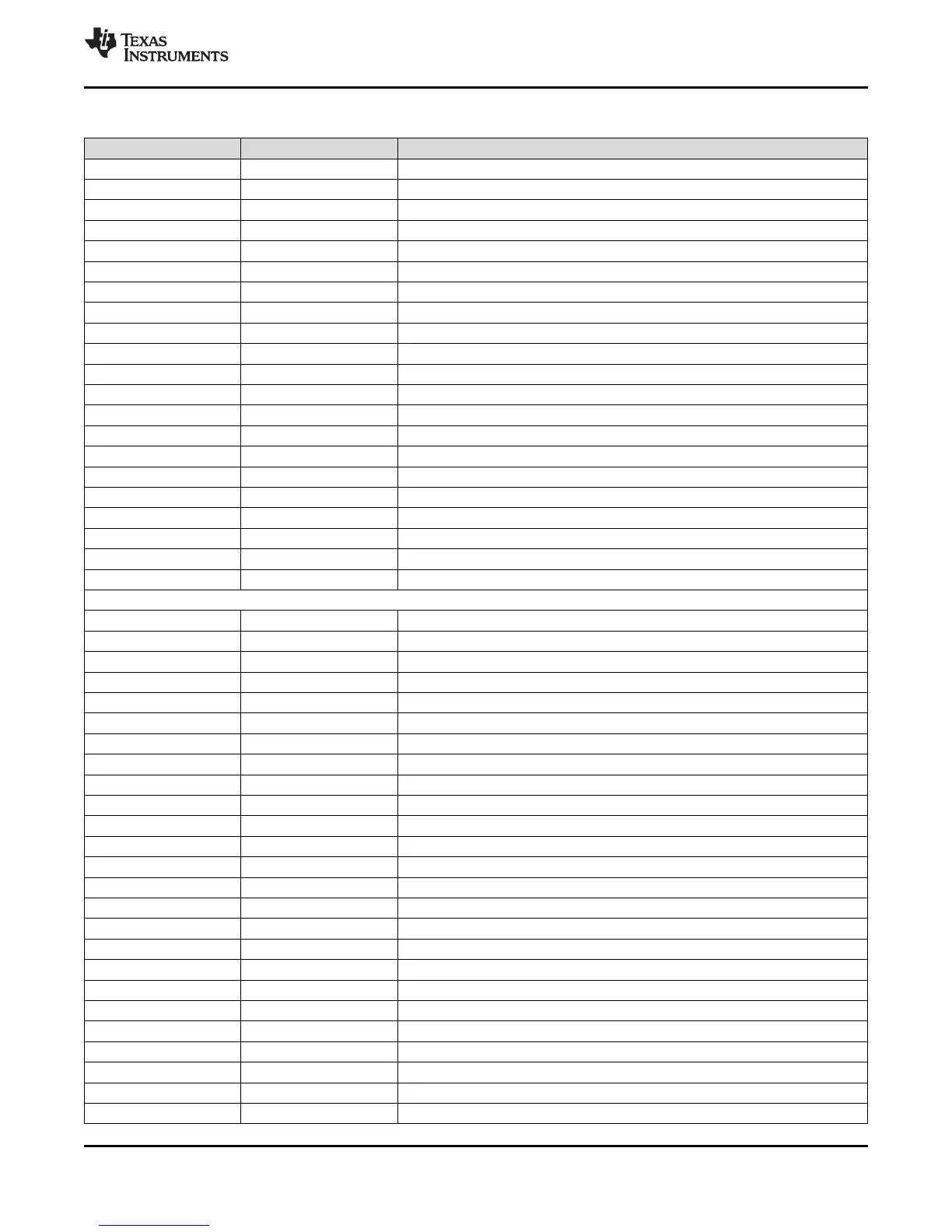

Table 6-90. Universal Serial Bus OTG (USB0) Registers (continued)

BYTE ADDRESS ACRONYM REGISTER DESCRIPTION

0x01E0 1800 TXGCR[0] Transmit Channel 0 Global Configuration Register

0x01E0 1808 RXGCR[0] Receive Channel 0 Global Configuration Register

0x01E0 180C RXHPCRA[0] Receive Channel 0 Host Packet Configuration Register A

0x01E0 1810 RXHPCRB[0] Receive Channel 0 Host Packet Configuration Register B

0x01E0 1820 TXGCR[1] Transmit Channel 1 Global Configuration Register

0x01E0 1828 RXGCR[1] Receive Channel 1 Global Configuration Register

0x01E0 182C RXHPCRA[1] Receive Channel 1 Host Packet Configuration Register A

0x01E0 1830 RXHPCRB[1] Receive Channel 1 Host Packet Configuration Register B

0x01E0 1840 TXGCR[2] Transmit Channel 2 Global Configuration Register

0x01E0 1848 RXGCR[2] Receive Channel 2 Global Configuration Register

0x01E0 184C RXHPCRA[2] Receive Channel 2 Host Packet Configuration Register A

0x01E0 1850 RXHPCRB[2] Receive Channel 2 Host Packet Configuration Register B

0x01E0 1860 TXGCR[3] Transmit Channel 3 Global Configuration Register

0x01E0 1868 RXGCR[3] Receive Channel 3 Global Configuration Register

0x01E0 186C RXHPCRA[3] Receive Channel 3 Host Packet Configuration Register A

0x01E0 1870 RXHPCRB[3] Receive Channel 3 Host Packet Configuration Register B

0x01E0 2000 DMA_SCHED_CTRL DMA Scheduler Control Register

0x01E0 2800 WORD[0] DMA Scheduler Table Word 0

0x01E0 2804 WORD[1] DMA Scheduler Table Word 1

. . . . . . . . .

0x01E0 28FC WORD[63] DMA Scheduler Table Word 63

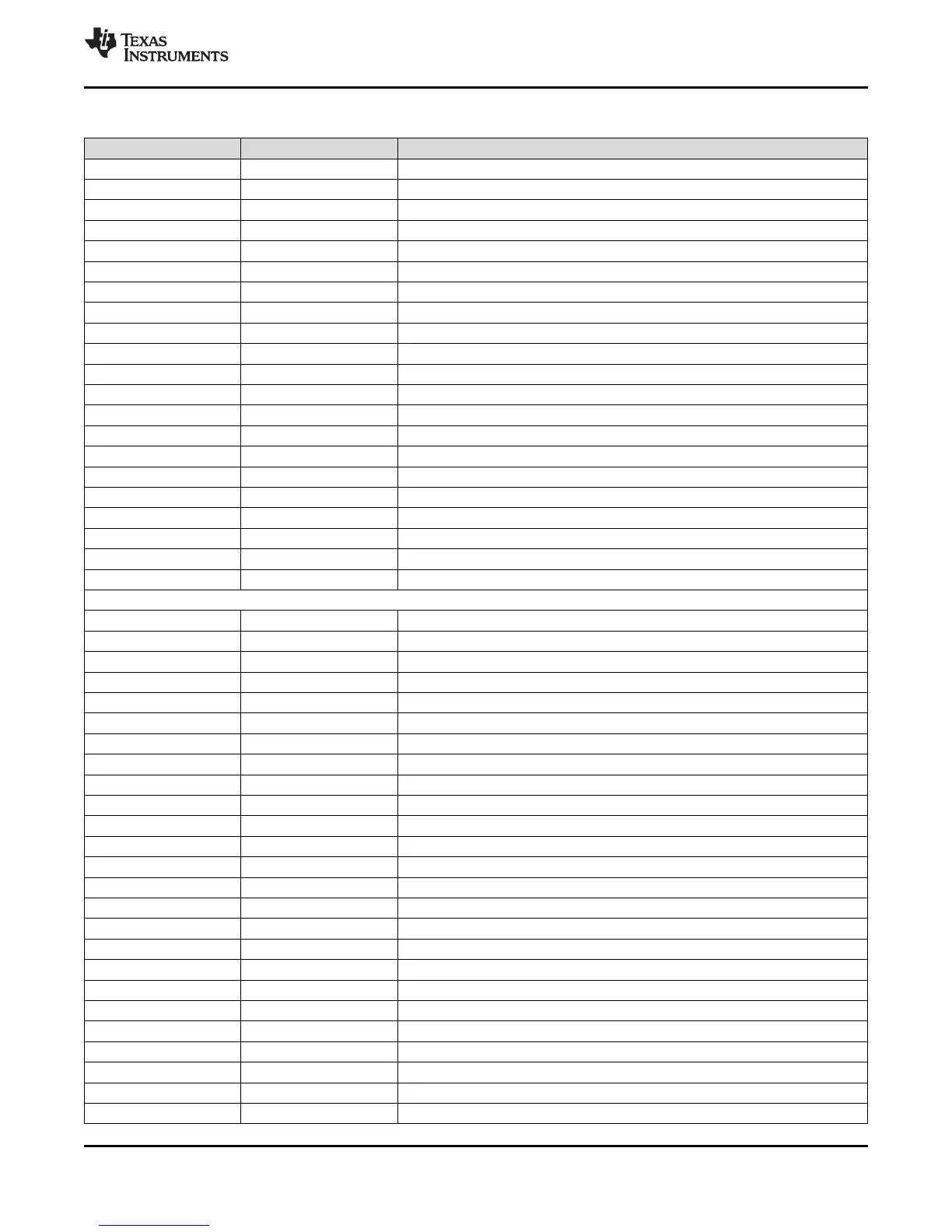

Queue Manager Registers

0x01E0 4000 QMGRREVID Queue Manager Revision Register

0x01E0 4008 DIVERSION Queue Diversion Register

0x01E0 4020 FDBSC0 Free Descriptor/Buffer Starvation Count Register 0

0x01E0 4024 FDBSC1 Free Descriptor/Buffer Starvation Count Register 1

0x01E0 4028 FDBSC2 Free Descriptor/Buffer Starvation Count Register 2

0x01E0 402C FDBSC3 Free Descriptor/Buffer Starvation Count Register 3

0x01E0 4080 LRAM0BASE Linking RAM Region 0 Base Address Register

0x01E0 4084 LRAM0SIZE Linking RAM Region 0 Size Register

0x01E0 4088 LRAM1BASE Linking RAM Region 1 Base Address Register

0x01E0 4090 PEND0 Queue Pending Register 0

0x01E0 4094 PEND1 Queue Pending Register 1

0x01E0 5000 QMEMRBASE[0] Memory Region 0 Base Address Register

0x01E0 5004 QMEMRCTRL[0] Memory Region 0 Control Register

0x01E0 5010 QMEMRBASE[1] Memory Region 1 Base Address Register

0x01E0 5014 QMEMRCTRL[1] Memory Region 1 Control Register

. . . . . . . . .

0x01E0 50F0 QMEMRBASE[15] Memory Region 15 Base Address Register

0x01E0 50F4 QMEMRCTRL[15] Memory Region 15 Control Register

0x01E0 600C CTRLD[0] Queue Manager Queue 0 Control Register D

0x01E0 601C CTRLD[1] Queue Manager Queue 1 Control Register D

. . . . . . . . .

0x01E0 63FC CTRLD[63] Queue Manager Queue 63 Status Register D

0x01E0 6800 QSTATA[0] Queue Manager Queue 0 Status Register A

0x01E0 6804 QSTATB[0] Queue Manager Queue 0 Status Register B

0x01E0 6808 QSTATC[0] Queue Manager Queue 0 Status Register C

Loading...

Loading...