230

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

www.ti.com

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Peripheral Information and Electrical Specifications Copyright © 2009–2017, Texas Instruments Incorporated

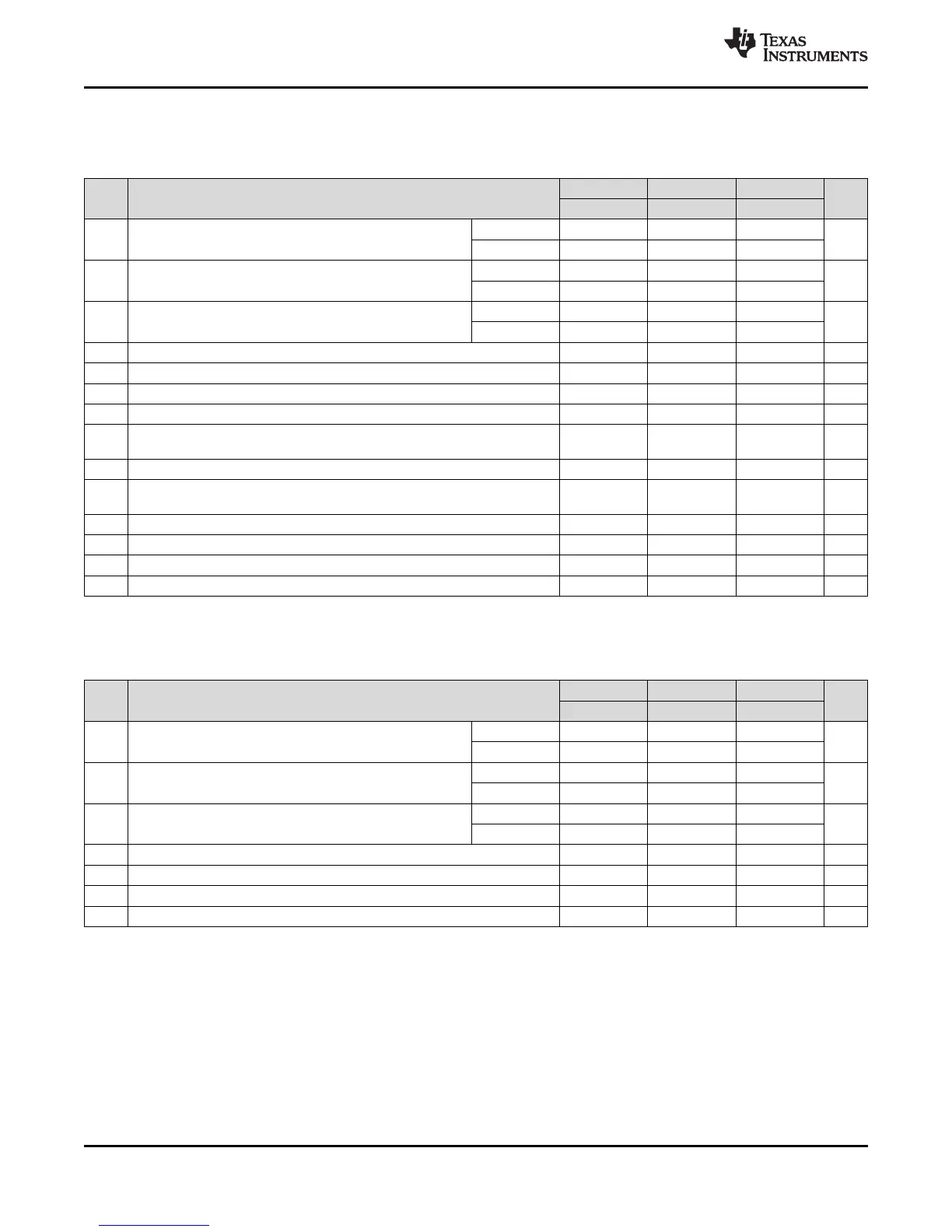

6.26.2 uPP Electrical Data/Timing

(1) 2xTXCLK is an alternate transmit clock source that must be at least 2 times the required uPP transmit clock rate (as it is is divided down

by 2 inside the uPP). 2xTXCLK has no specified skew relationship to the CHn_CLOCK and therefore is not shown in the timing diagram.

Table 6-116. Timing Requirements for uPP (see Figure 6-71, Figure 6-72, Figure 6-73, Figure 6-74)

NO.

1.3V, 1.2V 1.1V 1.0V

UNIT

MIN MAX MIN MAX MIN MAX

1 t

c(INCLK)

Cycle time, CHn_CLK

SDR mode 13.33 20 26.66

ns

DDR mode 26.66 40 53.33

2 t

w(INCLKH)

Pulse width, CHn_CLK high

SDR mode 5 8 10

ns

DDR mode 10 16 20

3 t

w(INCLKL)

Pulse width, CHn_CLK low

SDR mode 5 8 10

ns

DDR mode 10 16 20

4 t

su(STV-INCLKH)

Setup time, CHn_START valid before CHn_CLK high 4 5.5 6.5 ns

5 t

h(INCLKH-STV)

Hold time, CHn_START valid after CHn_CLK high 0.8 0.8 0.8 ns

6 t

su(ENV-INCLKH)

Setup time, CHn_ENABLE valid before CHn_CLK high 4 5.5 6.5 ns

7 t

h(INCLKH-ENV)

Hold time, CHn_ENABLE valid after CHn_CLK high 0.8 0.8 0.8 ns

8 t

su(DV-INCLKH)

Setup time,

CHn_DATA/XDATA valid before CHn_CLK high

4 5.5 6.5 ns

9 t

h(INCLKH-DV)

Hold time, CHn_DATA/XDATA valid after CHn_CLK high 0.8 0.8 0.8 ns

10 t

su(DV-INCLKL)

Setup time, CHn_DATA/XDATA valid before CHn_CLK

low

4 5.5 6.5 ns

11 t

h(INCLKL-DV)

Hold time, CHn_DATA/XDATA valid after CHn_CLK low 0.8 0.8 0.8 ns

19 t

su(WTV-INCLKL)

Setup time, CHn_WAIT valid before CHn_CLK high 10 12 14 ns

20 t

h(INCLKL-WTV)

Hold time, CHn_WAIT valid after CHn_CLK high 0.8 0.8 0.8 ns

21 t

c(2xTXCLK)

Cycle time, 2xTXCLK input clock

(1)

6.66 10 13.33 ns

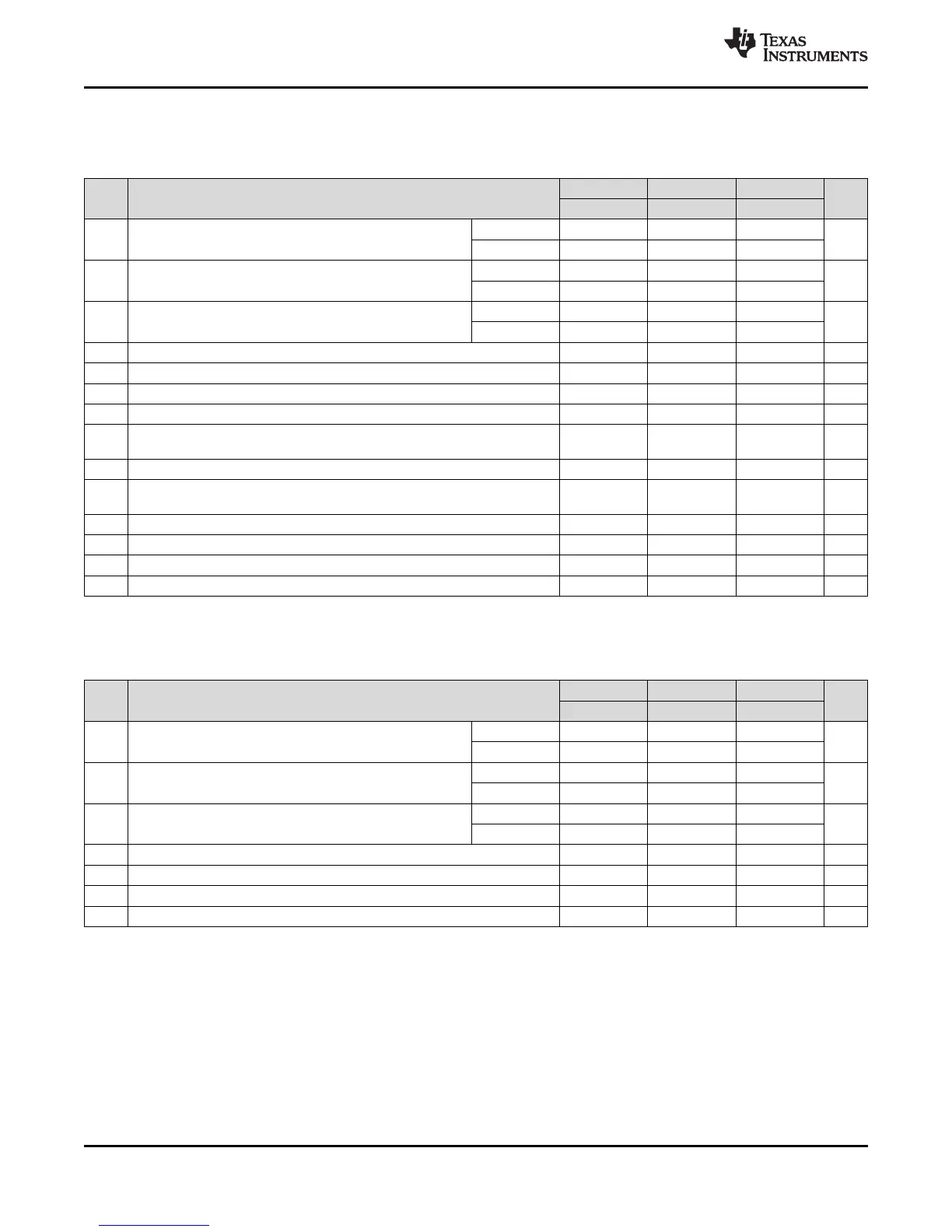

Table 6-117. Switching Characteristics Over Recommended Operating Conditions for uPP

NO. PARAMETER

1.3V, 1.2V 1.1V 1.0V

UNIT

MIN MAX MIN MAX MIN MAX

12 t

c(OUTCLK)

Cycle time, CHn_CLK

SDR mode 13.33 20 26.66

ns

DDR mode 26.66 40 53.33

13 t

w(OUTCLKH)

Pulse width, CHn_CLK high

SDR mode 5 8 10

ns

DDR mode 10 16 20

14 t

w(OUTCLKL)

Pulse width, CHn_CLK low

SDR mode 5 8 10

ns

DDR mode 10 16 20

15 t

d(OUTCLKH-STV)

Delay time, CHn_START valid after CHn_CLK high 2 11 2 15 2 21 ns

16 t

d(OUTCLKH-ENV)

Delay time, CHn_ENABLE valid after CHn_CLK high 2 11 2 15 2 21 ns

17 t

d(OUTCLKH-DV)

Delay time, CHn_DATA/XDATA valid after CHn_CLK high 2 11 2 15 2 21 ns

18 t

d(OUTCLKL-DV)

Delay time, CHn_DATA/XDATA valid after CHn_CLK low 2 11 2 15 2 21 ns

Loading...

Loading...