65

TMS320C6748

www.ti.com

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Device ComparisonCopyright © 2009–2017, Texas Instruments Incorporated

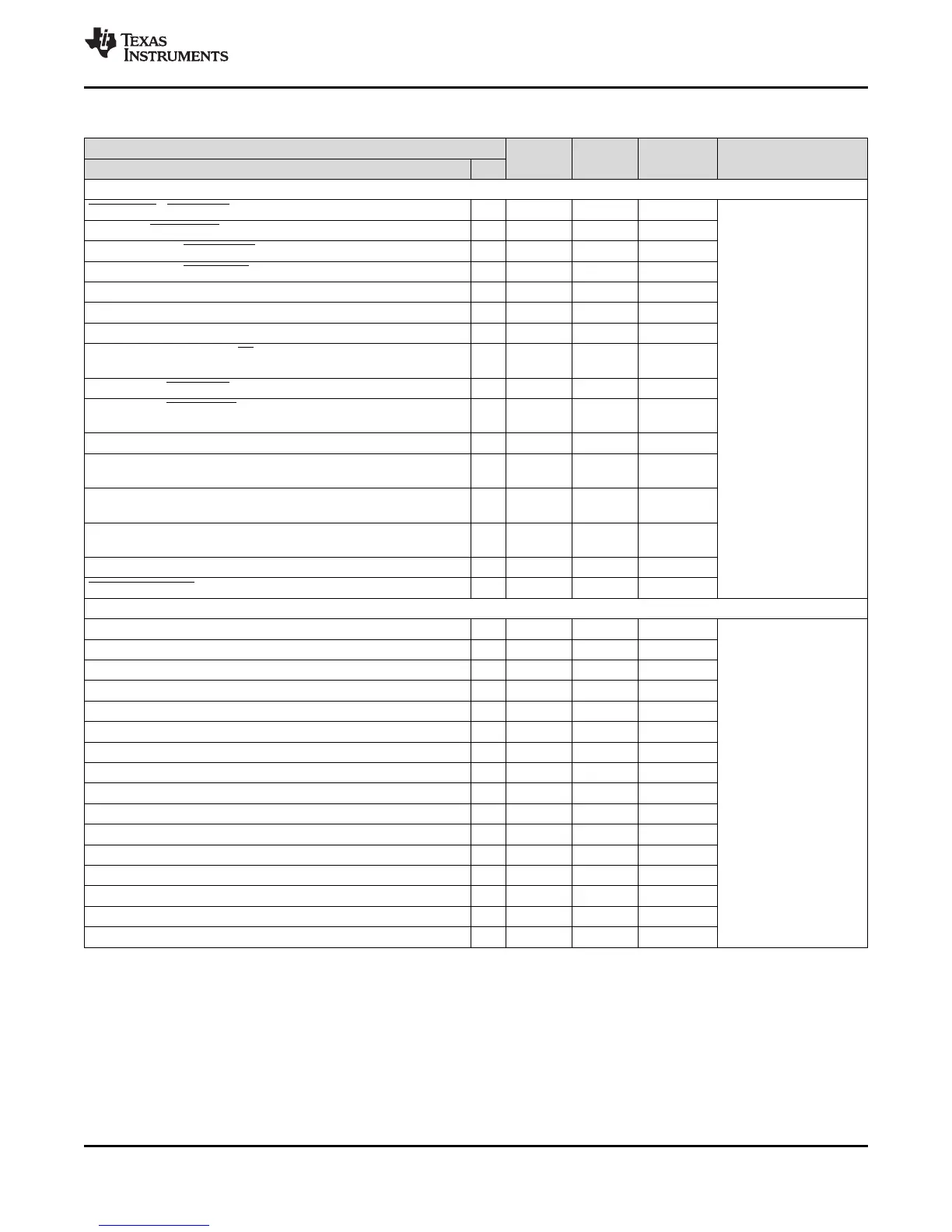

Table 3-29. General Purpose Input Output Terminal Functions (continued)

SIGNAL

TYPE

(1)

PULL

(2)

POWER

GROUP

(3)

DESCRIPTION

NAME NO.

GP6

RESETOUT / UHPI_HAS / PRU1_R30[14] / GP6[15] T17 I/O CP[21] C

GPIO Bank 6

CLKOUT / UHPI_HDS2 / PRU1_R30[13] / GP6[14] T18 I/O CP[22] C

PRU0_R30[31] / UHPI_HRDY / PRU1_R30[12] / GP6[13] R17 I/O CP[23] C

PRU0_R30[30] / UHPI_HINT / PRU1_R30[11] / GP6[12] R16 I/O CP[23] C

PRU0_R30[29] / UHPI_HCNTL0 / UPP_CHA_CLOCK / GP6[11] U17 I/O CP[24] C

PRU0_R30[28] / UHPI_HCNTL1 / UPP_CHA_START / GP6[10] W15 I/O CP[24] C

PRU0_R30[27] / UHPI_HHWIL / UPP_CHA_ENABLE / GP6[9] U16 I/O CP[24] C

PRU0_R30[26] / UHPI_HRW / UPP_CHA_WAIT/GP6[8] /

PRU1_R31[17]

T15 I/O CP[24] C

VP_CLKIN0 / UHPI_HCS / PRU1_R30[10] GP6[7] / UPP_2xTXCLK W14 I/O CP[25] C

VP_CLKIN1 / UHPI_HDS1 / PRU1_R30[9] / GP6[6] /

PRU1_R31[16]

V15 I/O CP[25] C

VP_DIN[8] / UHPI_HD[0] / UPP_D[0] / GP6[5] / PRU1_R31[0] P17 I/O CP[27] C

VP_CLKIN2 / MMCSD1_DAT[3] / PRU1_R30[3] / GP6[4] /

PRU1_R31[4]

H3 I/O CP[30] C

VP_CLKOUT2 / MMCSD1_DAT[2] / PRU1_R30[2] / GP6[3] /

PRU1_R31[3]

K3 I/O CP[30] C

VP_CLKIN3 / MMCSD1_DAT[1] / PRU1_R30[1] / GP6[2] /

PRU1_R31[2]

J3 I/O CP[30] C

VP_CLKOUT3 / PRU1_R30[0] / GP6[1] / PRU1_R31[1] K4 I/O CP[30] C

LCD_AC_ENB_CS / GP6[0] / PRU1_R31[28] R5 I/O CP[31] C

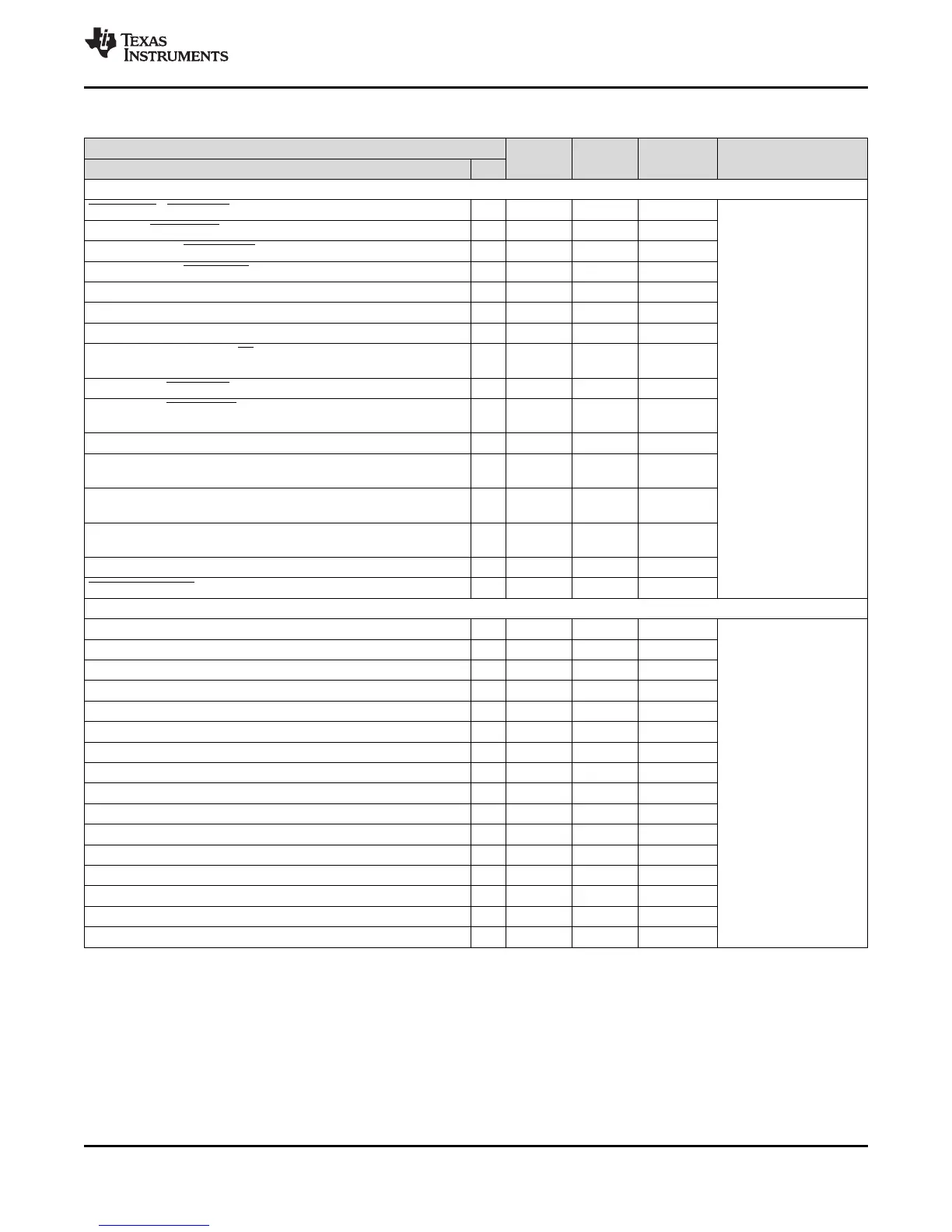

GP7

VP_DOUT[7] / LCD_D[7] / UPP_XD[15] / GP7[15] / PRU1_R31[15] U2 I/O CP[28] C

GPIO Bank 7

VP_DOUT[6] / LCD_D[6] / UPP_XD[14] / GP7[14] / PRU1_R31[14] U1 I/O CP[28] C

VP_DOUT[5] / LCD_D[5] / UPP_XD[13] / GP7[13] / PRU1_R31[13] V3 I/O CP[28] C

VP_DOUT[4] / LCD_D[4] / UPP_XD[12] / GP7[12] / PRU1_R31[12] V2 I/O CP[28] C

VP_DOUT[3] / LCD_D[3] / UPP_XD[11] / GP7[11] / PRU1_R31[11] V1 I/O CP[28] C

VP_DOUT[2] / LCD_D[2] / UPP_XD[10] / GP7[10] / PRU1_R31[10] W3 I/O CP[28] C

VP_DOUT[1] / LCD_D[1] / UPP_XD[9] / GP7[9] / PRU1_R31[9] W2 I/O CP[28] C

VP_DOUT[0] / LCD_D[0] / UPP_XD[8] / GP7[8] / PRU1_R31[8] W1 I/O CP[28] C

VP_DOUT[15] / LCD_D[15] / UPP_XD[7] / GP7[7] / BOOT[7] P4 I/O CP[29] C

VP_DOUT[14] / LCD_D[14] / UPP_XD[6] / GP7[6] / BOOT[6] R3 I/O CP[29] C

VP_DOUT[13] / LCD_D[13] / UPP_XD[5] / GP7[5]/ BOOT[5] R2 I/O CP[29] C

VP_DOUT[12] / LCD_D[12] / UPP_XD[4] / GP7[4] / BOOT[4] R1 I/O CP[29] C

VP_DOUT[11] / LCD_D[11] / UPP_XD[3] / GP7[3] / BOOT[3] T3 I/O CP[29] C

VP_DOUT[10] / LCD_D[10] / UPP_XD[2] / GP7[2] / BOOT[2] T2 I/O CP[29] C

VP_DOUT[9] / LCD_D[9] / UPP_XD[1] / GP7[1] / BOOT[1] T1 I/O CP[29] C

VP_DOUT[8] / LCD_D[8] / UPP_XD[0] / GP7[0] / BOOT[0] U3 I/O CP[29] C

Loading...

Loading...