98

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

www.ti.com

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Peripheral Information and Electrical Specifications Copyright © 2009–2017, Texas Instruments Incorporated

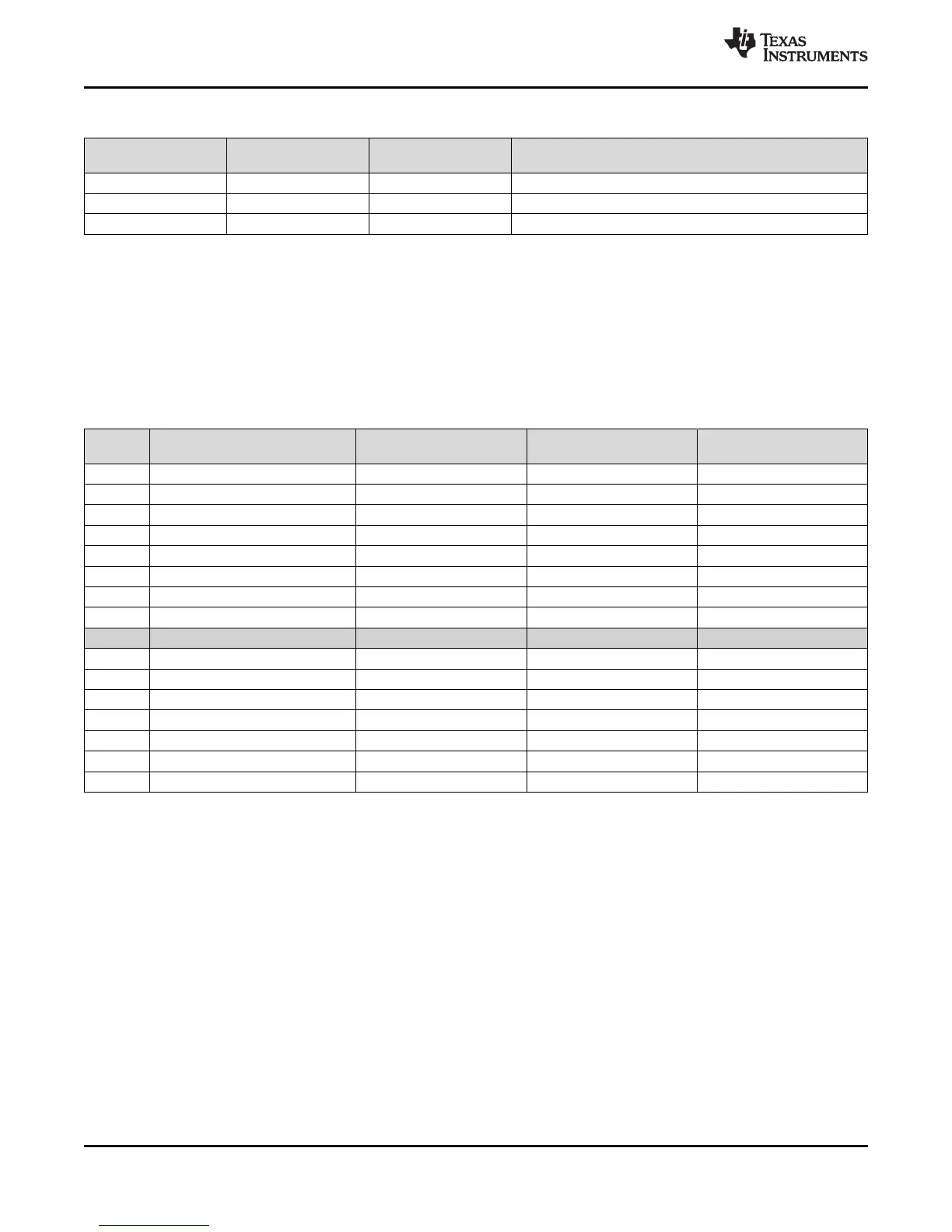

Table 6-8. Power and Sleep Controller (PSC) Registers (continued)

PSC0 BYTE

ADDRESS

PSC1 BYTE

ADDRESS

ACRONYM REGISTER DESCRIPTION

- 0x01E2 7A74 MDCTL29 Module 29 Control Register

- 0x01E2 7A78 MDCTL30 Module 30 Control Register

- 0x01E2 7A7C MDCTL31 Module 31 Control Register

6.8.1 Power Domain and Module Topology

The device includes two PSC modules.

Each PSC module controls clock states for several of the on chip modules, controllers and interconnect

components. Table 6-9 and Table 6-10 lists the set of peripherals/modules that are controlled by the PSC,

the power domain they are associated with, the LPSC assignment and the default (power-on reset)

module states. The module states and terminology are defined in Section 6.8.1.2.

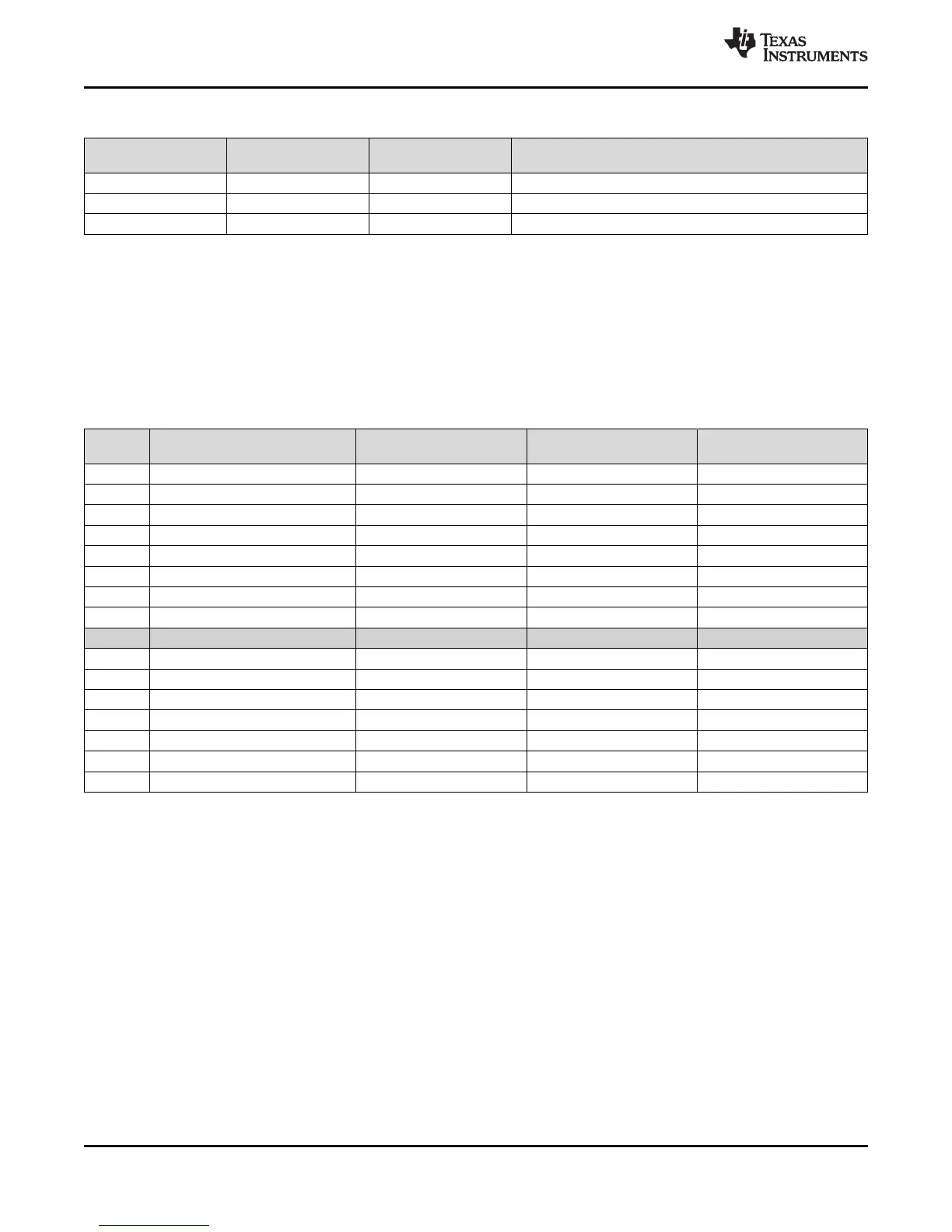

Table 6-9. PSC0 Default Module Configuration

LPSC

Number

Module Name Power Domain Default Module State Auto Sleep/Wake Only

0 EDMA3 Channel Controller 0 AlwaysON (PD0) SwRstDisable —

1 EDMA3 Transfer Controller 0 AlwaysON (PD0) SwRstDisable —

2 EDMA3 Transfer Controller 1 AlwaysON (PD0) SwRstDisable —

3 EMIFA (Br7) AlwaysON (PD0) SwRstDisable —

4 SPI 0 AlwaysON (PD0) SwRstDisable —

5 MMC/SD 0 AlwaysON (PD0) SwRstDisable —

6 — — — —

7 — — — —

8 — — — —

9 UART 0 AlwaysON (PD0) SwRstDisable —

10 SCR0 (Br 0, Br 1, Br 2, Br 8) AlwaysON (PD0) Enable Yes

11 SCR1 (Br 4) AlwaysON (PD0) Enable Yes

12 SCR2 (Br 3, Br 5, Br 6) AlwaysON (PD0) Enable Yes

13 PRUSS AlwaysON (PD0) SwRstDisable —

14 — — — —

15 DSP PD_DSP (PD1) Enable —

Loading...

Loading...