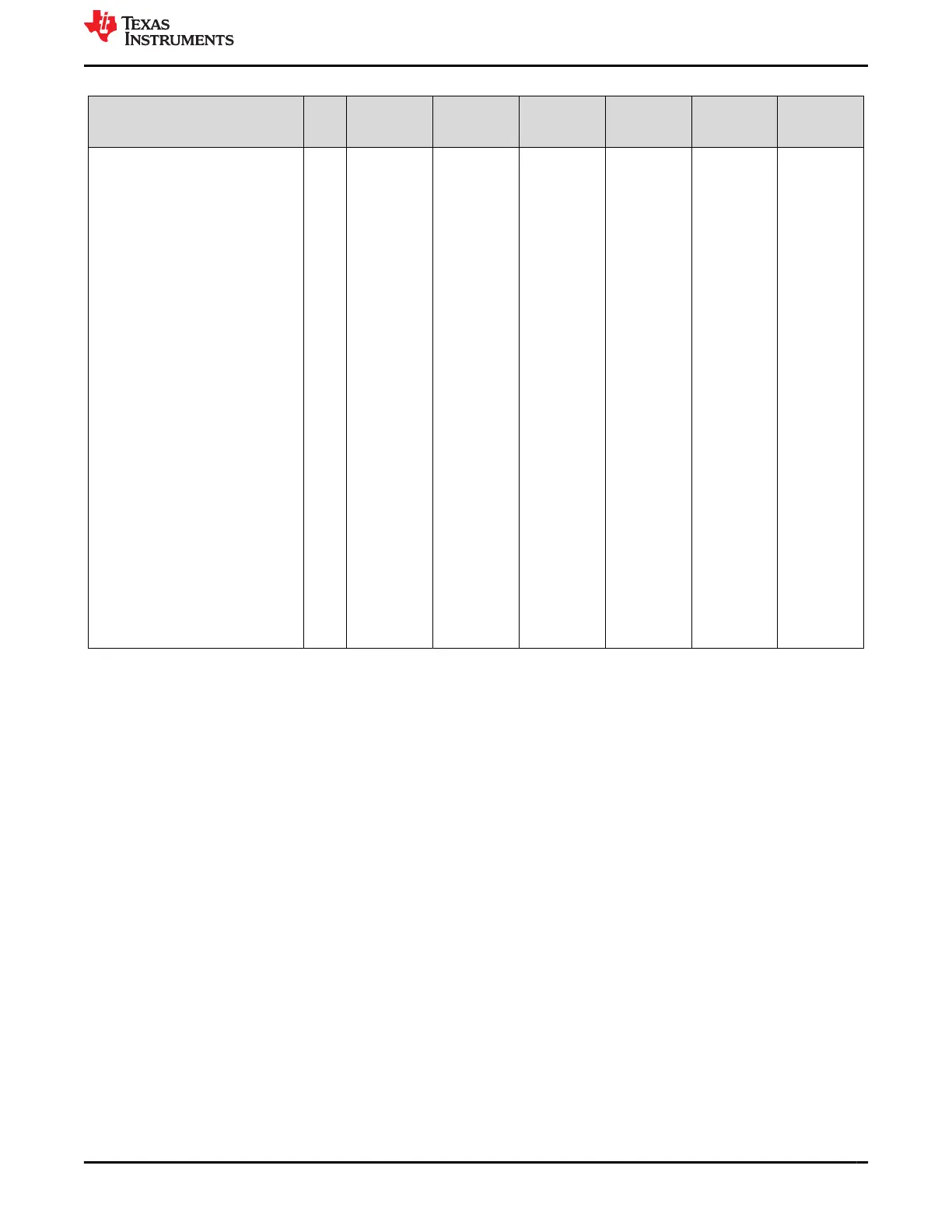

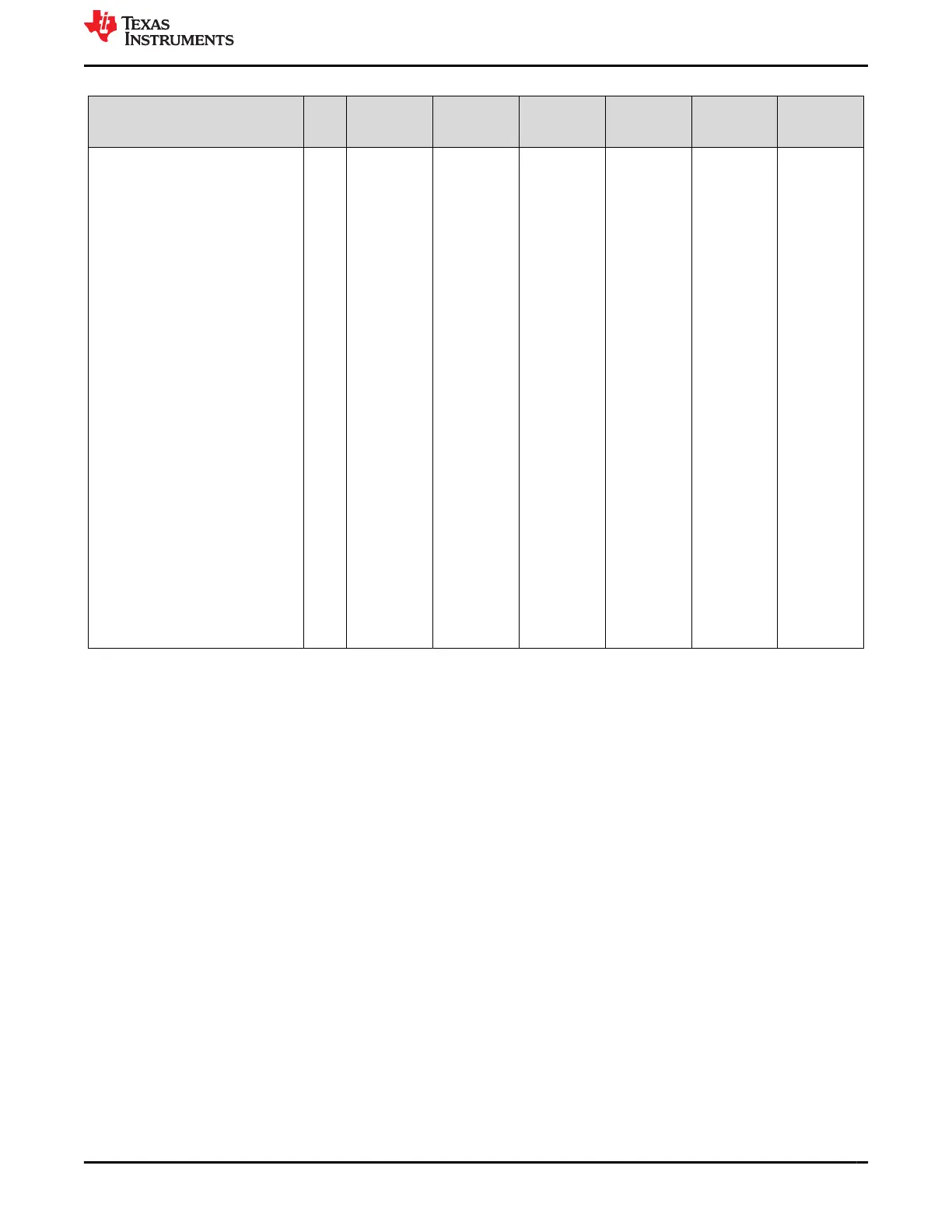

Table 2-1. Dual TPS6594-Q1 Orderable Part Numbers for Independent MCU and Main PDN System

PDN USE CASE PDN Orderable

Part Number

TI_NVM_ID

(TI_NVM_RE

V)

Orderable

Part Number

TI_NVM_ID

(TI_NVM_RE

V)

Orderable

Part Number

TI_NVM_ID(T

I_NVM_REV)

• Up to 9 A

(1)

on the Primary PMIC

3-phase CPU rail

• Up to 12 A

(1)

on the Secondary

PMIC 4-phase CORE rail

• Up to 3.4 A

(1)

on the SDRAM,

with support for LPDDR4

• Supports Processor 2 GHz

maximum clock with high-speed

SERDES operations

• Supports 32 Gb of LPDDR4

SDRAM with 4266MTs data rate

• Supports Functional Safety up to

ASIL-D level with MCU Safety

Island

• Supports MCU-only and

Retention low power modes

• Supports I/O level of 3.3 V or 1.8

V

• Supports optional end product

features:

– Compliant high-speed SD

Card memory

– Compliant USB 2.0 Interface

– On-board Efuse

programming of high security

processors

0A TPS65941120

RWERQ1

0x20 (0x04) TPS6594142

1 RWERQ1

0x21 (0x02)

LP876411B5

RQKRQ1

0xB5 (0x02)

(1) TI recommends having 15% margin between the maximum expected load current and the maximum current allowed per each PMIC

output rail.

www.ti.com Device Versions

SLVUCJ9 – FEBRUARY 2023

Submit Document Feedback

TPS65941120-Q1, TPS65941421-Q1 and LP876411B5-Q1 PMIC User Guide

for J721S2, PDN-0A

3

Copyright © 2023 Texas Instruments Incorporated

Loading...

Loading...