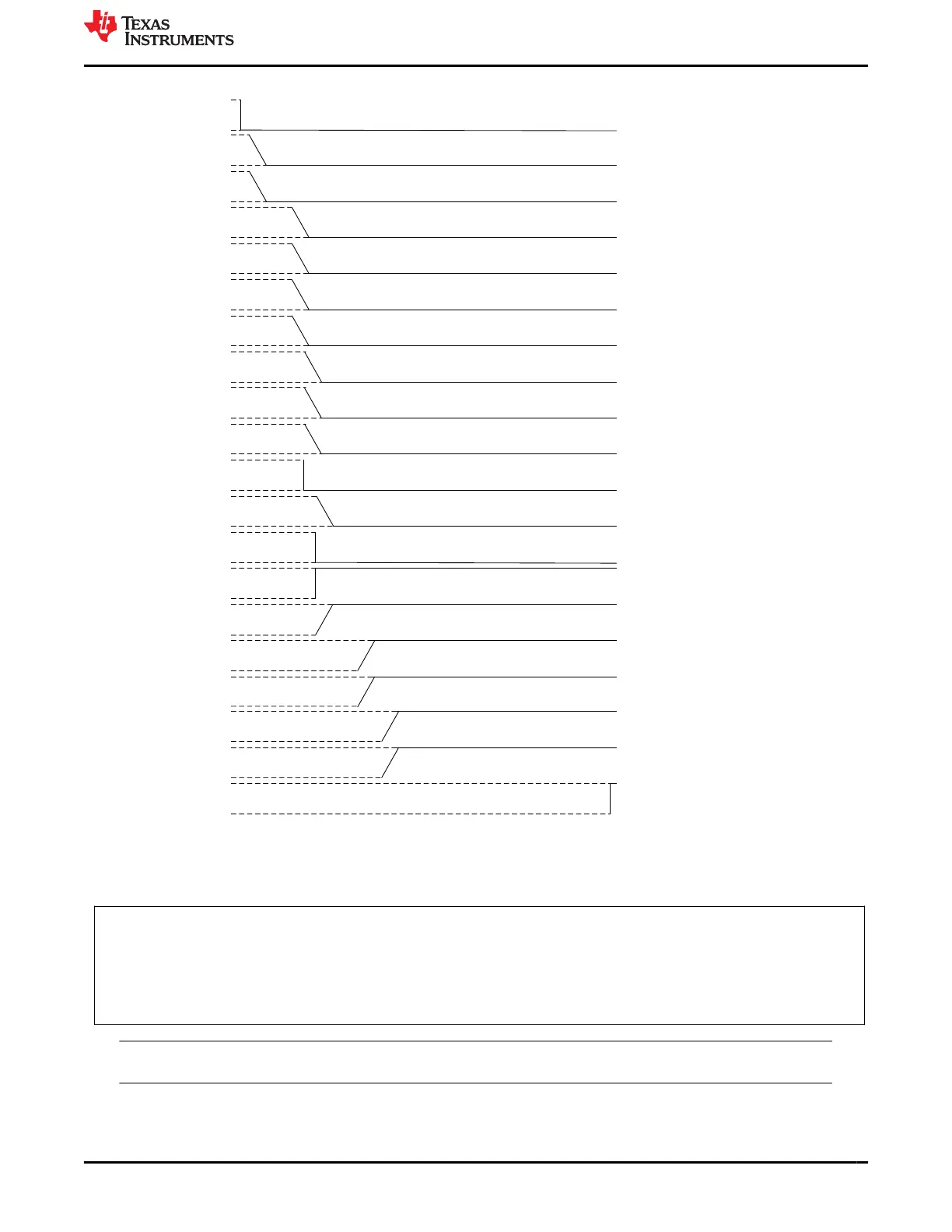

Resource PMIC Delay Diagram Total Delay Rail Name

GPIO9

TPS65941120-Q1

(Leo A)

3500 us EN_MCU3V3_VIO

LDO2

TPS65941120-Q1

(Leo A)

3500 us

VDD_MCU_

GPIORET_3V3

LDO2

TPS65941421-Q1

(Leo B)

3500 us VDD_GPIORET_3V3

GPIO3

TPS65941421-Q1

(Leo B)

3000 us EN_DDR_VDD1

LDO4

TPS65941120-Q1

(Leo A)

5200 us VDA_MCU_1V8

LDO3

TPS65941120-Q1

(Leo A)

5200 us VDD_MCUIO_1V8

BUCK5

TPS65941120-Q1

(Leo A)

6200 us VDD_MCU_0V85

LDO1

TPS65941120-Q1

(Leo A)

6200 us VDD_MCU_WK_0V8

LDO1

TPS65941421-Q1

(Leo B)

2500 us VDD_WK_0V8

BUCK4

TPS65941421-Q1

(Leo B)

500 us VDD_DDR_1V1

nRSTOUT

TPS65941120-Q1

(Leo A)

16200 us H_MCU_PORz

FSM I2C Trigger

GPIO11

TPS65941120-Q1

(Leo A)

0 us

H_SOC_PORz

(nRSTOUT_SOC)

BUCK5

TPS65941421-Q1

(Leo B)

500 us VDD_RAM_0V85

LDO3

TPS65941421-Q1

(Leo B)

2500 us VDA_DLL_0V8

BUCK1234

LP876411B5-Q1

(Hera C)

2500 us VDD_CORE_0V8

BUCK1234

TPS65941120-Q1

(Leo A)

2500 us VDD_CPU_AVS

LDO4

TPS65941421-Q1

(Leo B)

3000 us VDD_PLL_1V8

BUCK1

TPS65941421-Q1

(Leo B)

3000 us VDD_IO_1V8

BUCK3

TPS65941421-Q1

(Leo B)

3000 us VDD_PHY_1V8

GPIO11

TPS65941421-Q1

(Leo B)

3500 us EN_3V3_VIO

I2C_6 = 0

I2C_7 = 0

I2C_6 = 0

I2C_7 = 0

Figure 6-10. TO_MCU Sequence with I2C Triggers low in both PMICs

The last instructions of the TO_MCU sequence also perform writes to the MISC_CTRL and

ENABLE_DRV_STAT registers after the delay defined in the PFSM_DELAY_REG_1.

// TPS659411120

SREG_READ_REG ADDR=0xCD REG=R1

DELAY_SREG R1

// Clear FORCE_EN_DRV_LOW

REG_WRITE_MASK_IMM ADDR=0x82 DATA=0x00 MASK=0xF7

// Set NRSTOUT (MCU_PORZ)

REG_WRITE_MASK_IMM ADDR=0x81 DATA=0x01 MASK=0xFE

Note

After the TO_MCU sequence the MCU is responsible for managing the EN_DRV.

www.ti.com Pre-Configurable Finite State Machine (PFSM) Settings

SLVUCJ9 – FEBRUARY 2023

Submit Document Feedback

TPS65941120-Q1, TPS65941421-Q1 and LP876411B5-Q1 PMIC User Guide

for J721S2, PDN-0A

45

Copyright © 2023 Texas Instruments Incorporated

Loading...

Loading...