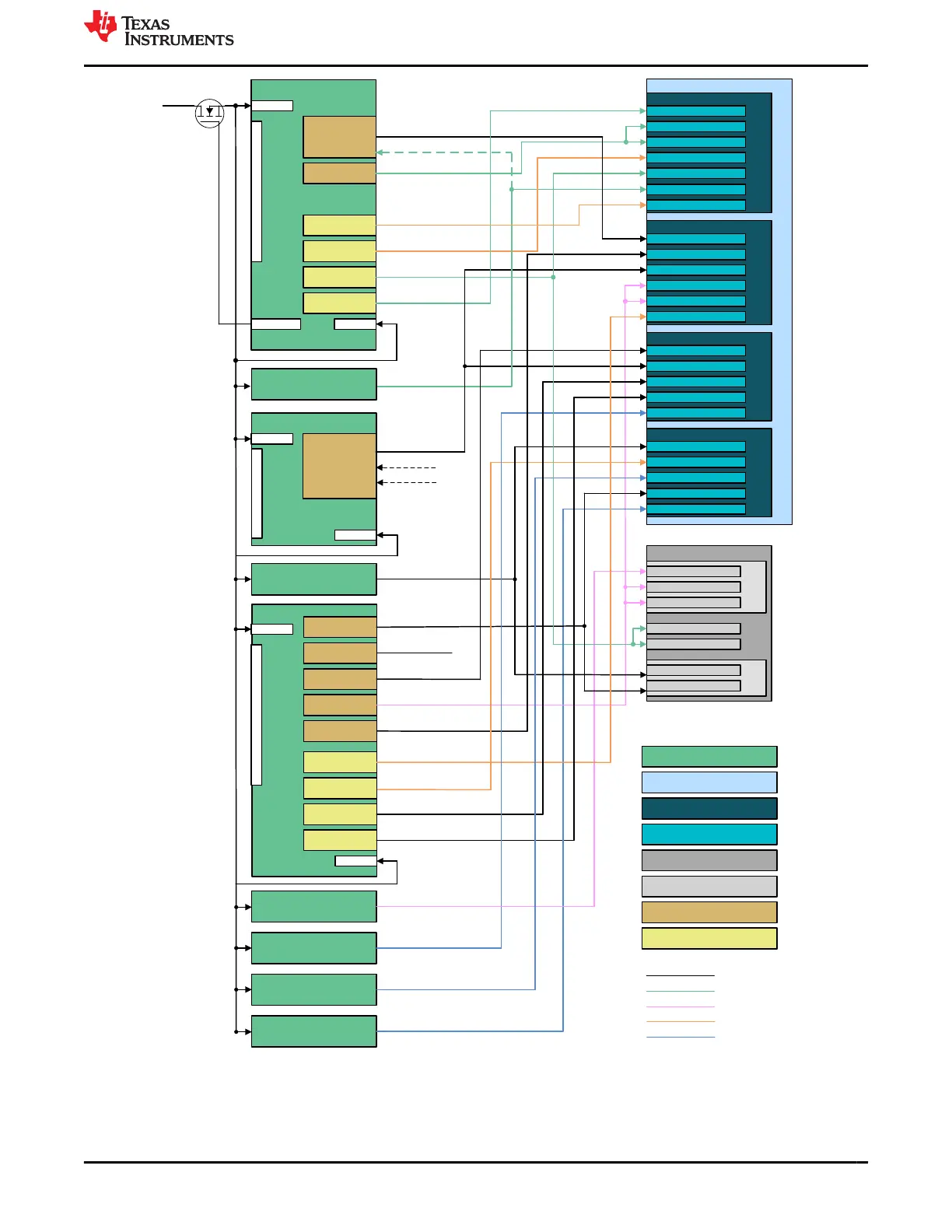

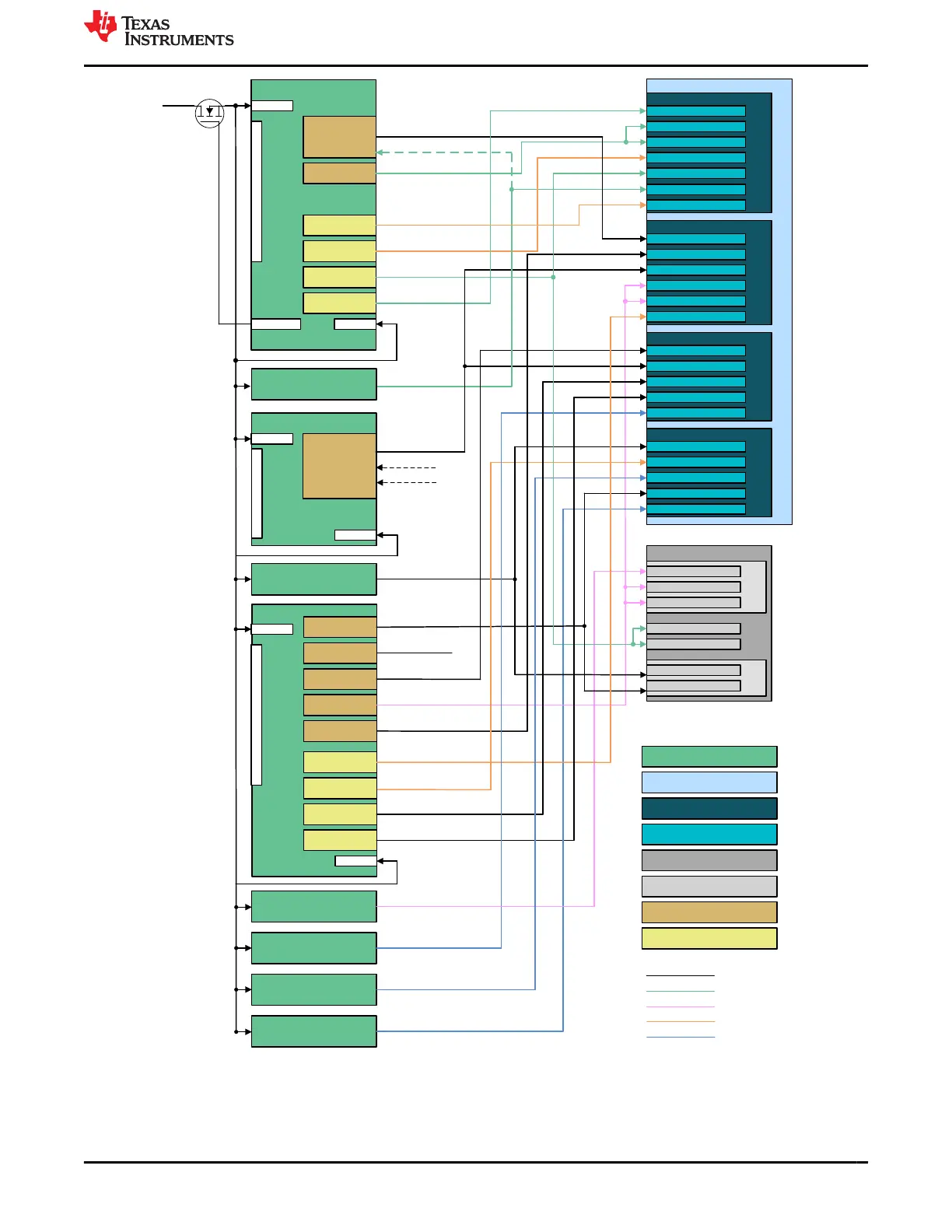

LPDDR4

TPS65941120-Q1

BUCK1+BUCK2+

BUCK3 + BUCK4

(14A max)

Primary PMIC

TPS65941421-Q1

Secondary PMIC

VDDA_x

MCU SAFETY ISLAND

Processor

VDDAR_MCU

VDD_MCU

VDDSHV0_MCU (3.3V)

VDDSHV1_MCU (1.8V)

VDD_CPU (AVS)

MAIN PROCESSOR

VDDAR_CPU/CORE

VDD_CORE

VDDS_DDR

VDDS_DDR_IO

VDD1

System

VDD2

VDDQ

PDN Features

Base PDN

MCU-Only

and Safety Island

DDR Retention

VCCA

VCCA

VIO_IN

VIO_IN

BUCK5

(2A max)

LDO1

(500mA max)

LDO2

(500mA max)

LDO3

(500mA max)

LDO4

(300mA max)

LDO1

(500mA max)

LDO2

(500mA max)

LDO3

(500mA max)

LDO4

(300mA max)

BUCK4

(4A max)

VSYS_3V3

OVPGDRV

VDDA_1P8_PHYs

MAIN ANALOG

VDDA_0P8_PHYs

VDDA_0P8_PLLs/DLLs

VDDA_1P8_PLLs

VDDA_3P3_USB

VDDSHV0

MAIN DIGITAL

VDDSHV2

VDDSHV5

VDDS_MMC0

VPP_x (EFUSE)

FLASH

HYPER FLASH

VDD_CPU_AVS*

FB_B3

VDD_MCU_0V85

VDD_MCUGPIORET_3V3

VDA_MCU_1V8

VDD_MCUWK_0v8

VDD_MCUIO_1V8

VDD_MCUIO_3V3

VDD_PRHL_TBD

VDD_DDR_1V1

VDD_RAM_0V85

VDD_WK_0V8

VDA_PLL_1V8

VDD_IO_3V3

VCCA_3V3

Tertiary PMIC

VCCA

VIO_IN

BUCK1+BUCK2+

BUCK3+BUCK4

(20A max)

LP876211B5-Q1

eMMC

VCC

VCCQ

End Product

Option

VDD_CORE_0V8

VDA_DLL_0V8

BUCK1

(4A max)

BUCK2

(4A max)

BUCK3

(4A max)

VDD_VDDIO_1V8

VDD_PHY_1V8

BUCK5

(4A max)

VDD_GPIORET_3V3

FB_B3

FB_B4

VDDSHV2_MCU (3.3V)

VDD_MCU_WAKE1

VDD_WAKE0

TPS22965-Q1

(Load Switch, 4A max)

TPS22965-Q1

(Load Switch, 4A max)

TLV73318P-Q1

(LDO, 300mA max)

TLV73333P-Q1

(LDO, 300mA max)

TLV103318-Q1

(LDO, 200mA max)

TLV3318P-Q1

(LDO, 300mA max)

Power Components

Processor Group

Processor Sub-group

Processor Supply Groups

System Group

System IO

Domain Descriptors

BUCK

LDO

VDD1_DDR_1V8

VDDA_3P3_USB

VDD_SD_DV**

VPP_EFUSE_1V8

GPIO Retention

Figure 3-1. Power Connections

• * VDD_CPU_AVS, boot voltage of 0.8 V then software sets device specific AVS; 0.68 V – 0.72 V.

• ** VDD_SD_DV, 3.3 V then software changes to 1.8 V per HS-SD.

www.ti.com Processor Connections

SLVUCJ9 – FEBRUARY 2023

Submit Document Feedback

TPS65941120-Q1, TPS65941421-Q1 and LP876411B5-Q1 PMIC User Guide

for J721S2, PDN-0A

5

Copyright © 2023 Texas Instruments Incorporated

Loading...

Loading...