40 www.xilinx.com ML505/ML506/ML507 Evaluation Platform

UG347 (v3.1.1) October 7, 2009

Chapter 1: ML505/ML506/ML507 Evaluation Platform

R

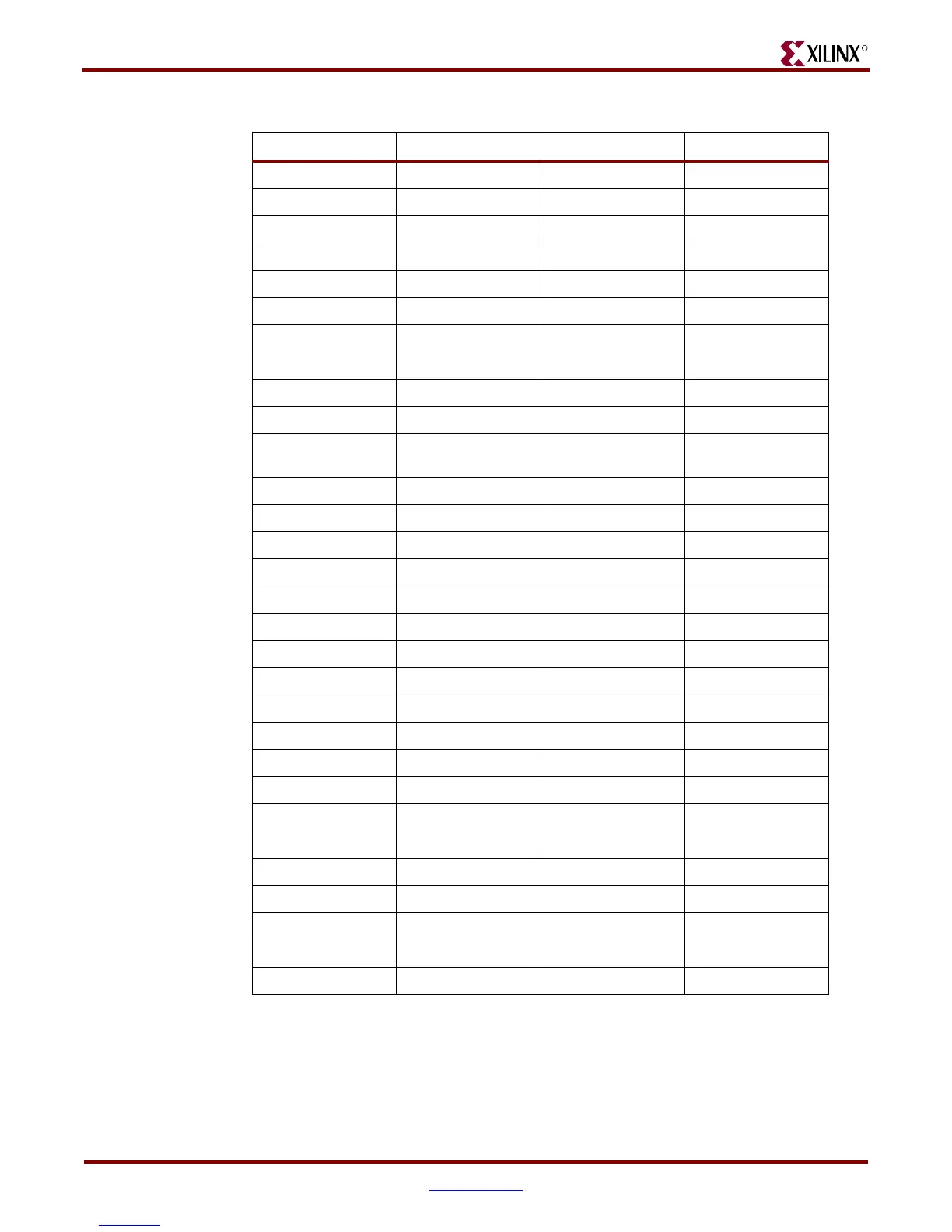

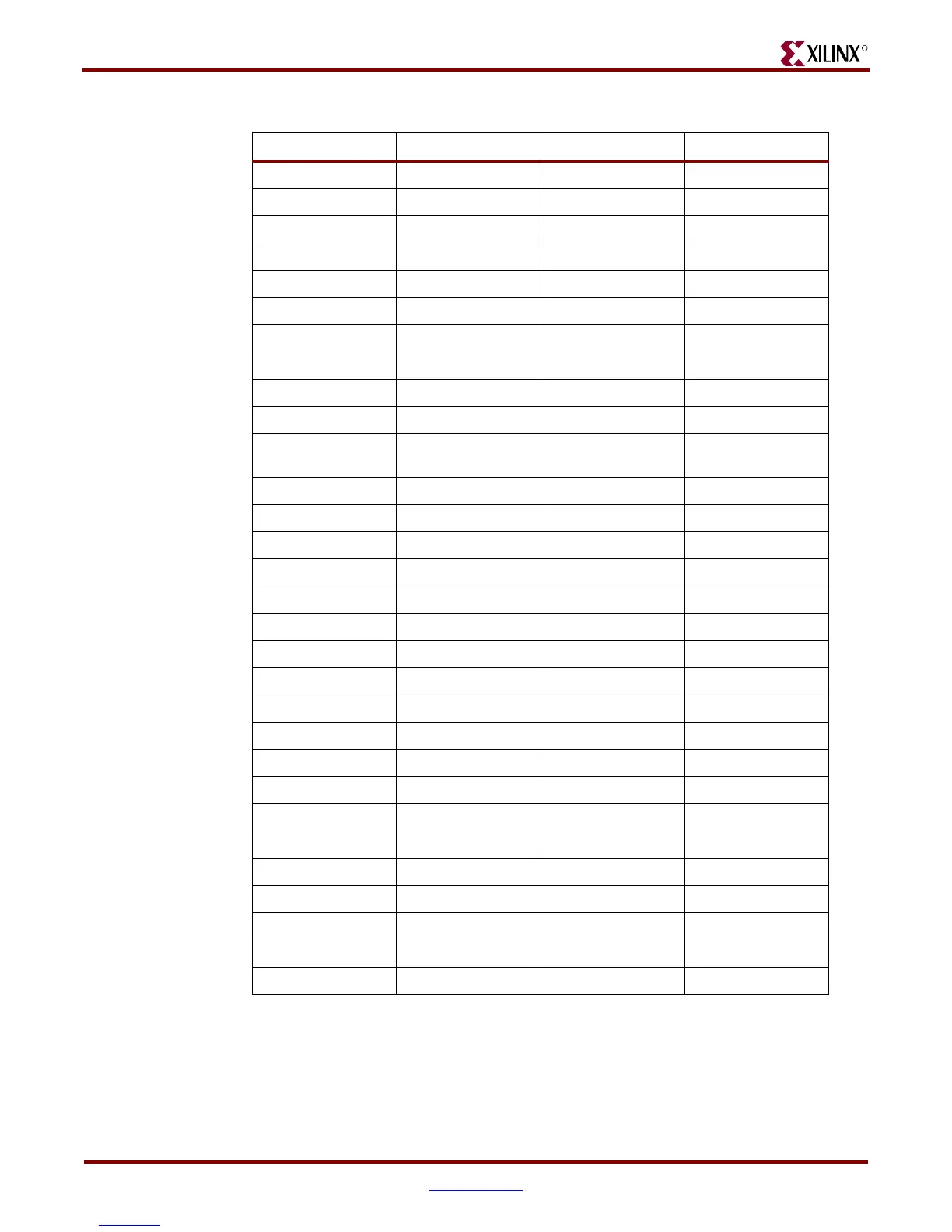

-NC9

-NC10

CPU_TDO E7 11 1

TRC_VSENSE - 12

-NC13

-NC14

CPU_TCK E6 15 7

MICTOR_16 B18 16

CPU_TMS U10 17 9

MICTOR_18 B17 18

FPGA_CS0_B

(CPU_TDI)

AF21 19 3

MICTOR_20 B16 20

CPU_TRST V10 21 4

MICTOR_22 B15 22

MICTOR_23 A23 23

TRC_TS1O AF10 24

MICTOR_25 A21 25

TRC_TS2O AF9 26

MICTOR_27 A20 27

TRC_TS1E AK9 28

MICTOR_29 A19 29

TRC_TS2E AK8 30

MICTOR_31 A18 31

TRC_TS3 AJ11 32

MICTOR_33 A16 33

TRC_TS4 AK11 34

MICTOR_35 A15 35

TRC_TS5 AD11 36

MICTOR_37 A14 37

TRC_TS6 AD10 38

Notes:

1. MICTOR_* pins are only available on the ML507 board. These pins are not connected on the

ML505 and ML506 boards.

Table 1-21: CPU Trace/Debug Connection to FPGA (Cont’d)

Pin Name

(1)

FPGA Pin (U1) Mictor Pin (P22) BDM Pin (J51)

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...