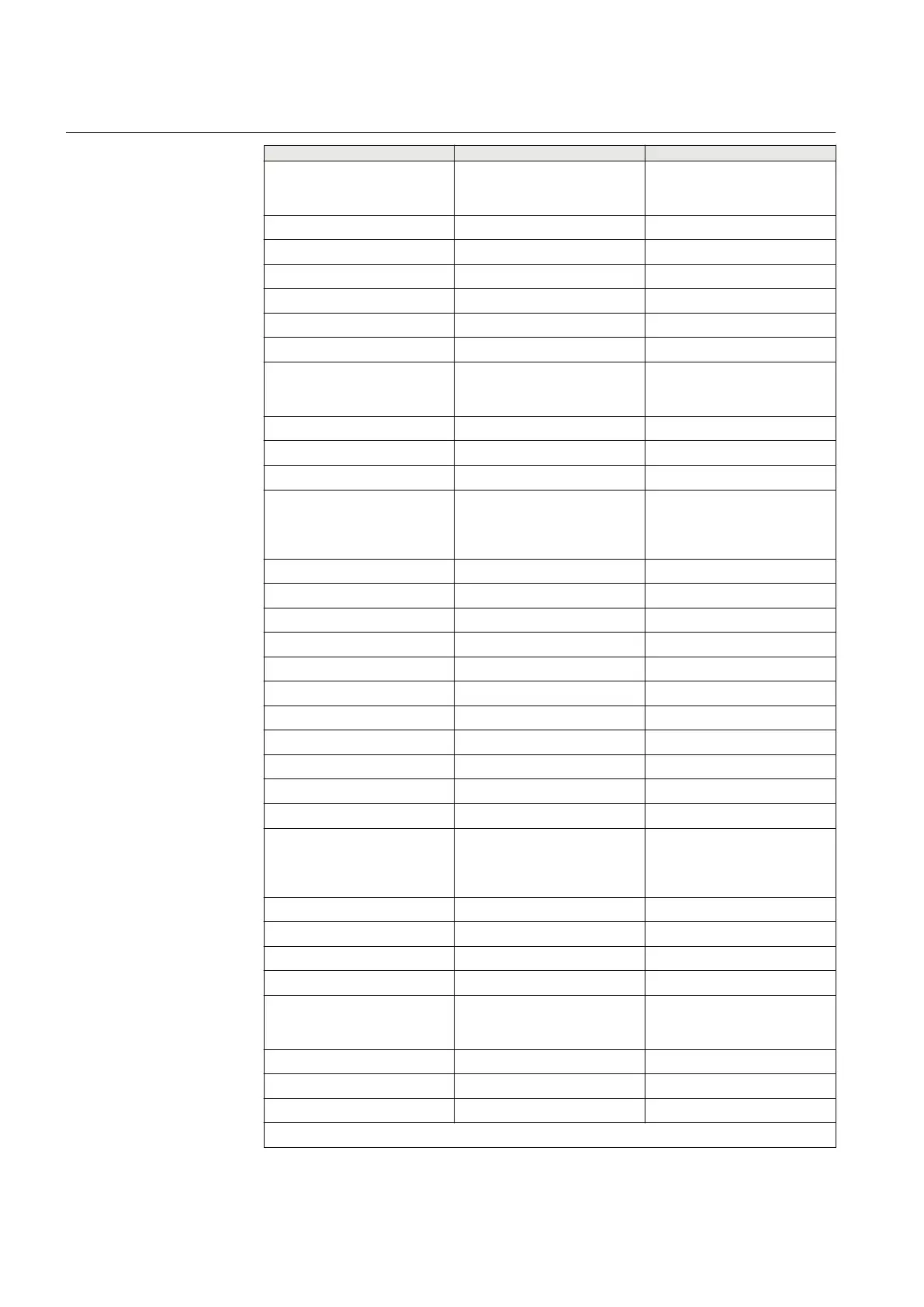

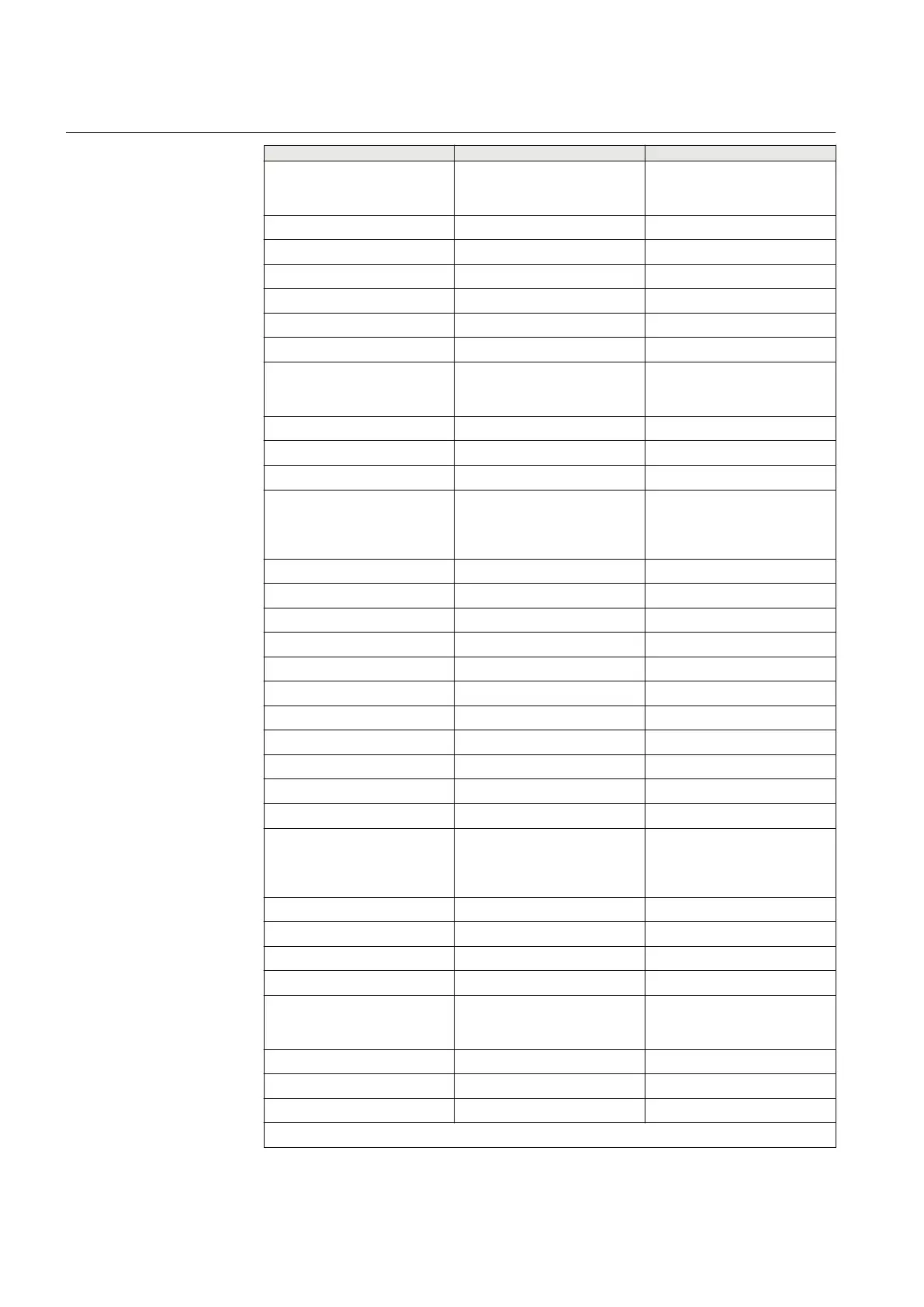

Function block name Edition 1 logical nodes Edition 2 logical nodes

OV2PTOV GEN2LLN0

OV2PTOV

PH1PTRC

OV2PTOV

PH1PTRC

PCFCNT PCGGIO PCFCNT

PHPIOC PHPIOC PHPIOC

QCBAY QCBAY BAY/LLN0

QCRSV QCRSV QCRSV

RCHLCCH RCHLCCH RCHLCCH

REFPDIF REFPDIF REFPDIF

ROV2PTOV GEN2LLN0

PH1PTRC

ROV2PTOV

PH1PTRC

ROV2PTOV

SCHLCCH SCHLCCH SCHLCCH

SCILO SCILO SCILO

SCSWI SCSWI SCSWI

SESRSYN RSY1LLN0

AUT1RSYN

MAN1RSYN

SYNRSYN

AUT1RSYN

MAN1RSYN

SYNRSYN

SLGAPC

SLGGIO SLGAPC

SMBRREC SMBRREC SMBRREC

SMPPTRC SMPPTRC SMPPTRC

SP16GAPC SP16GGIO SP16GAPC

SPC8GAPC SPC8GGIO SPC8GAPC

SPGAPC SPGGIO SPGAPC

SSCBR SSCBR SSCBR

SSIMG SSIMG SSIMG

SSIML SSIML SSIML

SXCBR SXCBR SXCBR

SXSWI SXSWI SXSWI

T3WPDIF T3WPDIF T3WGAPC

T3WPDIF

T3WPHAR

T3WPTRC

TEIGAPC

TEIGGIO TEIGAPC

TEILGAPC TEILGGIO TEILGAPC

TMAGAPC TMAGGIO TMAGAPC

TRPTTR TRPTTR TRPTTR

UV2PTUV GEN2LLN0

PH1PTRC

UV2PTUV

PH1PTRC

UV2PTUV

VMMXU VMMXU VMMXU

VMSQI VMSQI VMSQI

VNMMXU VNMMXU VNMMXU

Table continues on next page

Section 1 1MRK 505 393-UEN B

Introduction

24 Line differential protection RED650 2.2 IEC

Application manual

Loading...

Loading...