30

7679H–CAN–08/08

AT90CAN32/64/128

address actually is driven on the bus. The access time cannot exceed the time from the ALE

pulse must be asserted low until data is stable during a read sequence (see t

LLRL

+ t

RLRH

- t

DVRH

in Table 26-7 through Table 26-14). The different wait-states are set up in software. As an addi-

tional feature, it is possible to divide the external memory space in two sectors with individual

wait-state settings. This makes it possible to connect two different memory devices with different

timing requirements to the same XMEM interface. For XMEM interface timing details, please

refer to Table 26-7 through Table 26-14 and Figure 26-6 to Figure 26-9 in the “External Data

Memory Characteristics” on page 375.

Note that the XMEM interface is asynchronous and that the waveforms in the following figures

are related to the internal system clock. The skew between the internal and external clock

(XTAL1) is not guarantied (varies between devices temperature, and supply voltage). Conse-

quently, the XMEM interface is not suited for synchronous operation.

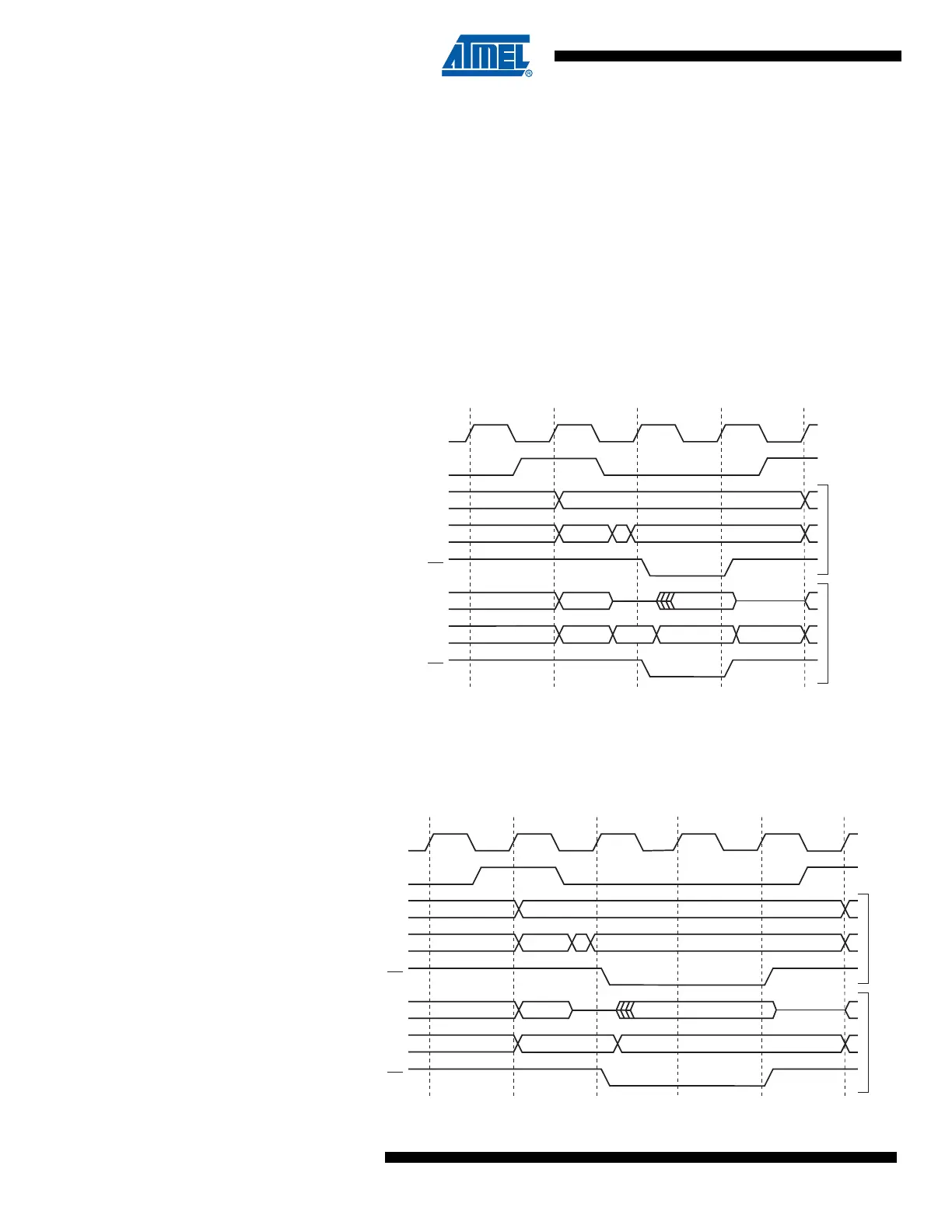

Figure 4-6. External Data Memory Cycles no Wait-state (SRWn1=0 and SRWn0=0)

(1)

Note: 1. SRWn1 = SRW11 (upper sector) or SRW01 (lower sector), SRWn0 = SRW10 (upper sector) or

SRW00 (lower sector). The ALE pulse in period T4 is only present if the next instruction

accesses the RAM (internal or external).

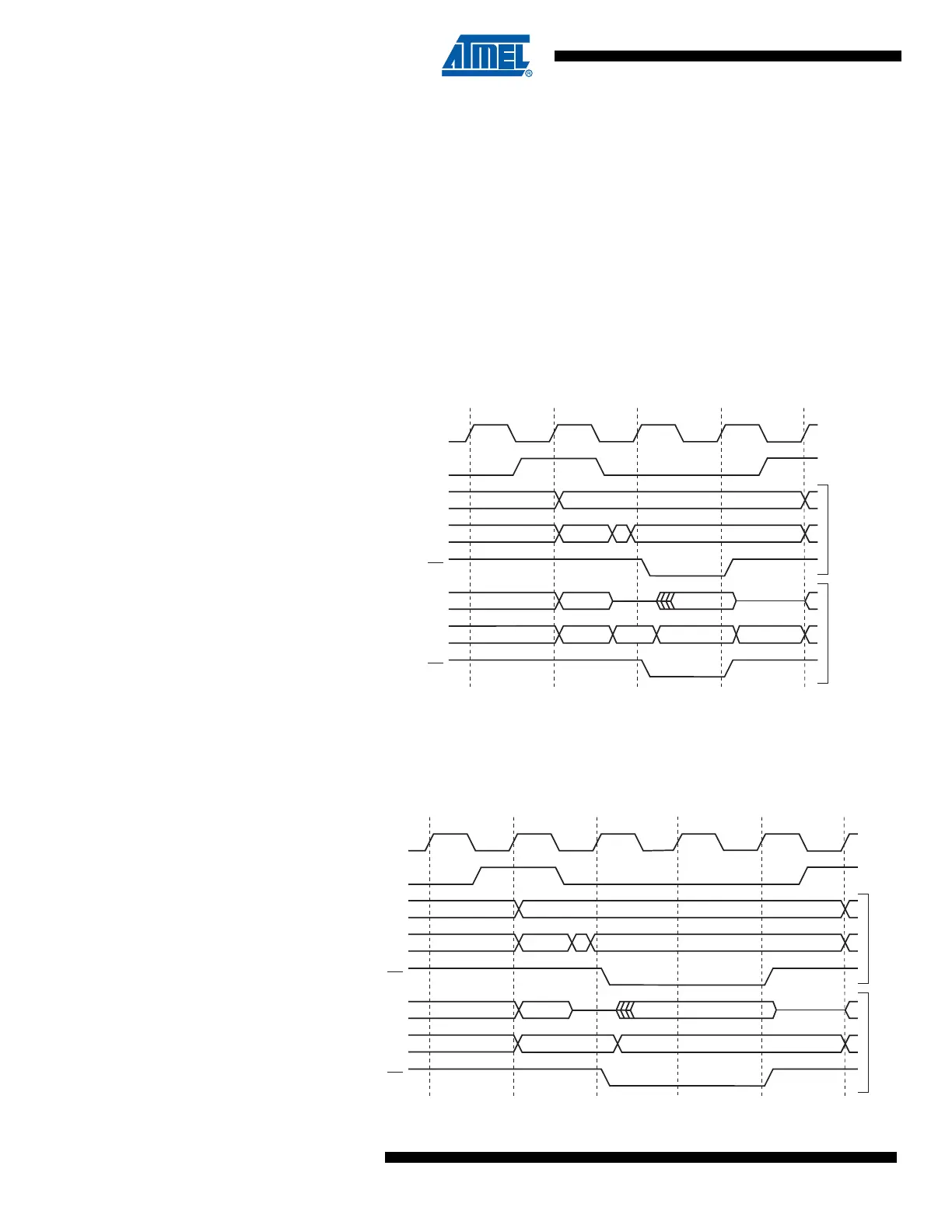

Figure 4-7. External Data Memory Cycles with SRWn1 = 0 and SRWn0 = 1

(1)

ALE

T1 T2 T3

Write

Read

WR

T4

A15:8

AddressPrev. addr.

DA7:0

Address DataPrev. data XX

RD

DA7:0 (XMBK = 0)

DataPrev. data Address

DataPrev. data Address

DA7:0 (XMBK = 1)

System Clock (CLK

CPU

)

XXXXX XXXXXXXX

ALE

T1 T2 T3

Write

Read

WR

T5

A15:8

AddressPrev. addr.

DA7:0

Address DataPrev. data XX

RD

DA7:0 (XMBK = 0)

DataPrev. data Address

DataPrev. data Address

DA7:0 (XMBK = 1)

System Clock (CLK

CPU

)

T4

Loading...

Loading...