FT800 Series Programmer Guide

Version 2.1

Document Reference No.: BRT_000030 Clearance No.: BRT#037

69

Product Page

Document Feedback Copyright © Bridgetek Limited

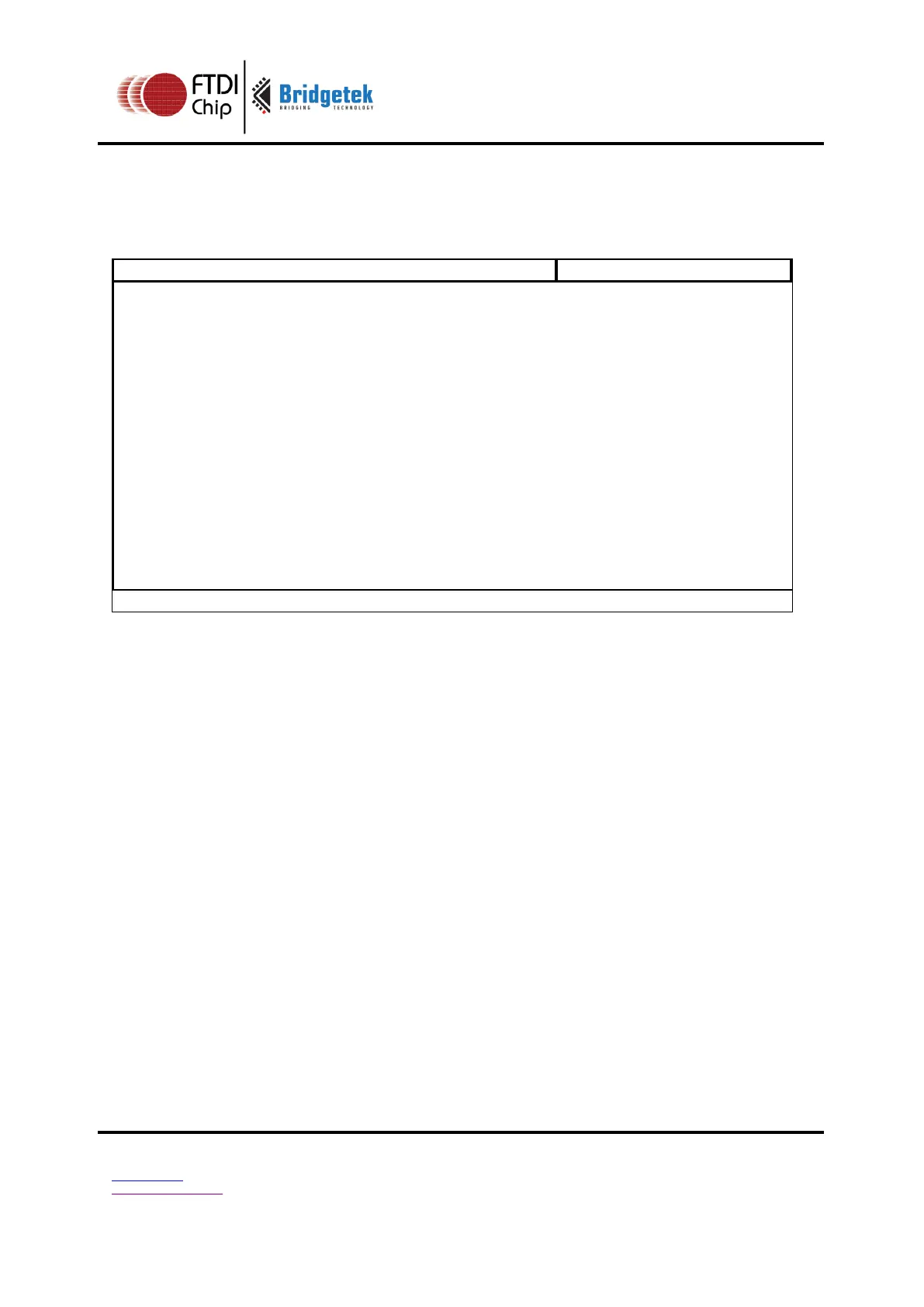

Register Definition 56 REG_CMD_READ Definition

Note: The host shall not write into this register unless in error recovery case.

Its default value is zero after the coprocessor engine is reset.

Bit 0 - 11 : These bits are updated by the coprocessor engine as long as the

coprocessor engine fetched the command from its FIFO. The host can read

this register to determine the FIFO fullness of the coprocessor engine. The

valid value range is from 0 to 4095. In the case of error, the coprocessor

engine writes 0xFFF to this register.

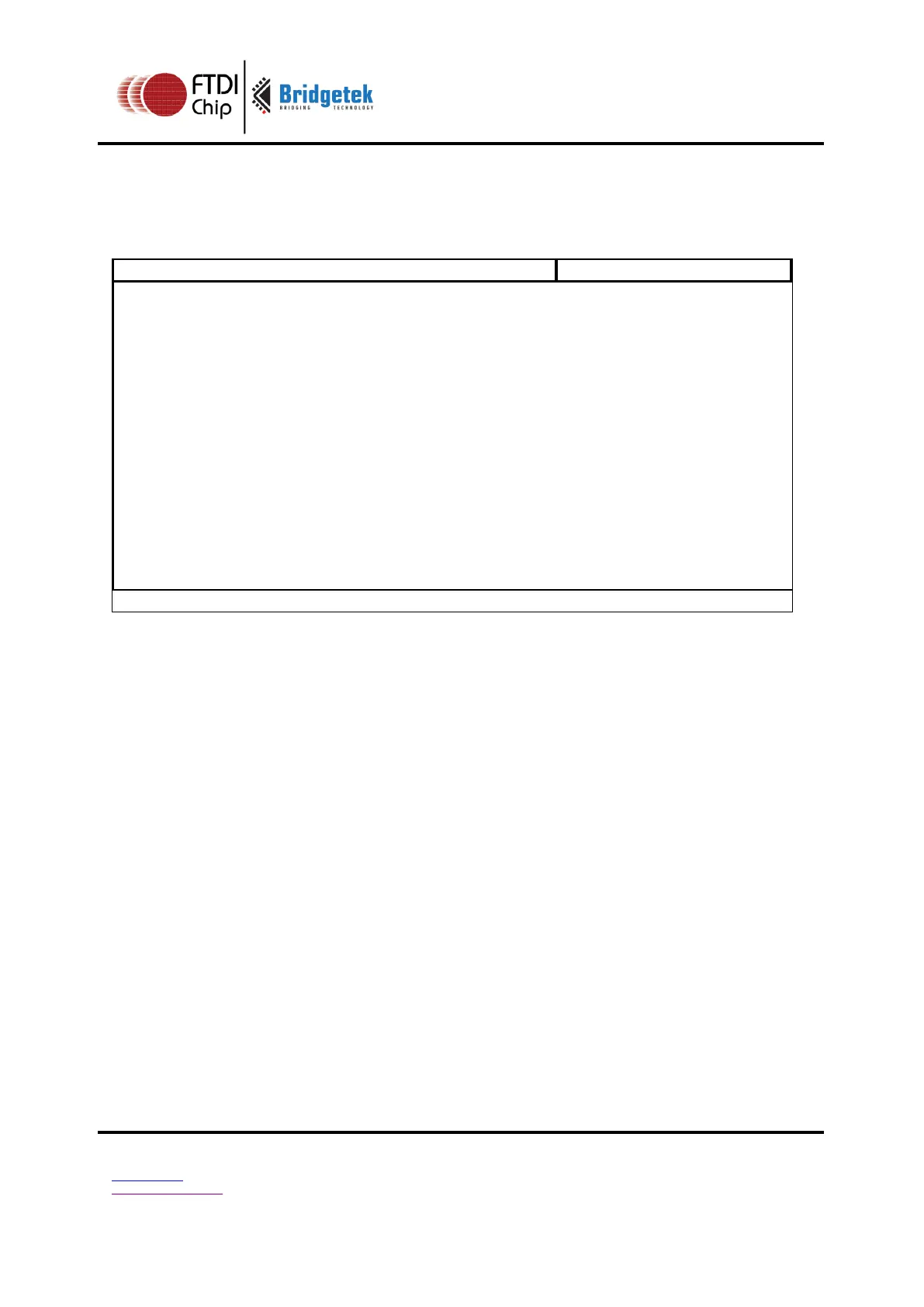

Register Definition 57 REG_TRACKER Definition

Loading...

Loading...