2.

The

result

register

is

reserved for the functional unit time

+(VL+2)

clock periods.

The

result

register

is

reserved for the

functional unit

+7

clock periods

if

the vector length

is

less than

5.

At

functional unit time

+2

(chain

slot

time) a subsequent

instruction,

which

has

met

all

other issue conditions,

may

issue.

This

process

is

called "chaining." Several

instructions

using

different

functional units

may

be

chained in

this

manner

to

attain

a

significant

enhancement of processing speed.

3. Vector operand

registers

are reserved for

VL

clock periods. Vector

operand

registers

are reserved for 5 clock periods

if

the vector

length

is

less

than 5.

The

vector

register

used

in a block

store

to

memory

(177

instruction)

is

reserved for

VL

clock periods. Scalar

operand

registers

are not reserved.

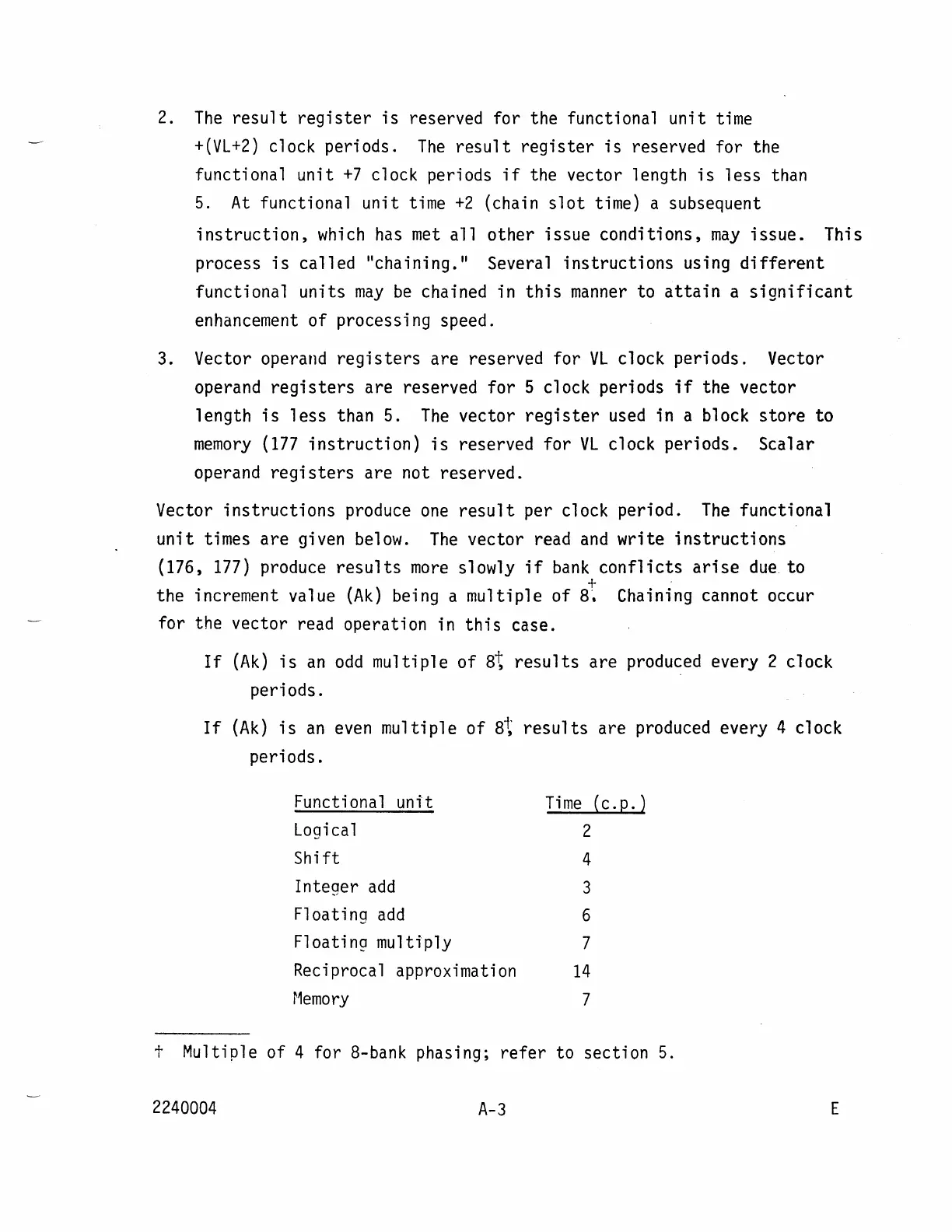

Vector

instructions

produce

one

result

per clock period.

The

functional

unit

times are given

below.

The

vector read

and

write

instructions

(176,

177)

produce

results

more

slowly

if

bank

conflicts

arise

due.

to

+

the increment value

(Ak)

being a multiple of

a~

Chaining cannot occur

for the vector read operation in

this

case.

If

(Ak)

is

an

odd

multiple of

at

results

are produced every 2 clock

periods.

If

(Ak)

is

an

even

multiple of

at

results

are produced every 4 clock

periods.

Functional unit

Time

(c.p.)

Logical 2

Shift

4

Integer

add

3

Floating

add

6

Floating multiply 7

Reciprocal approximation

14

r1emory

7

t Multiple of 4 for a-bank phasing;

refer

to section

5.

2240004

A-3

E

Loading...

Loading...