REMOTE CONTROL

185

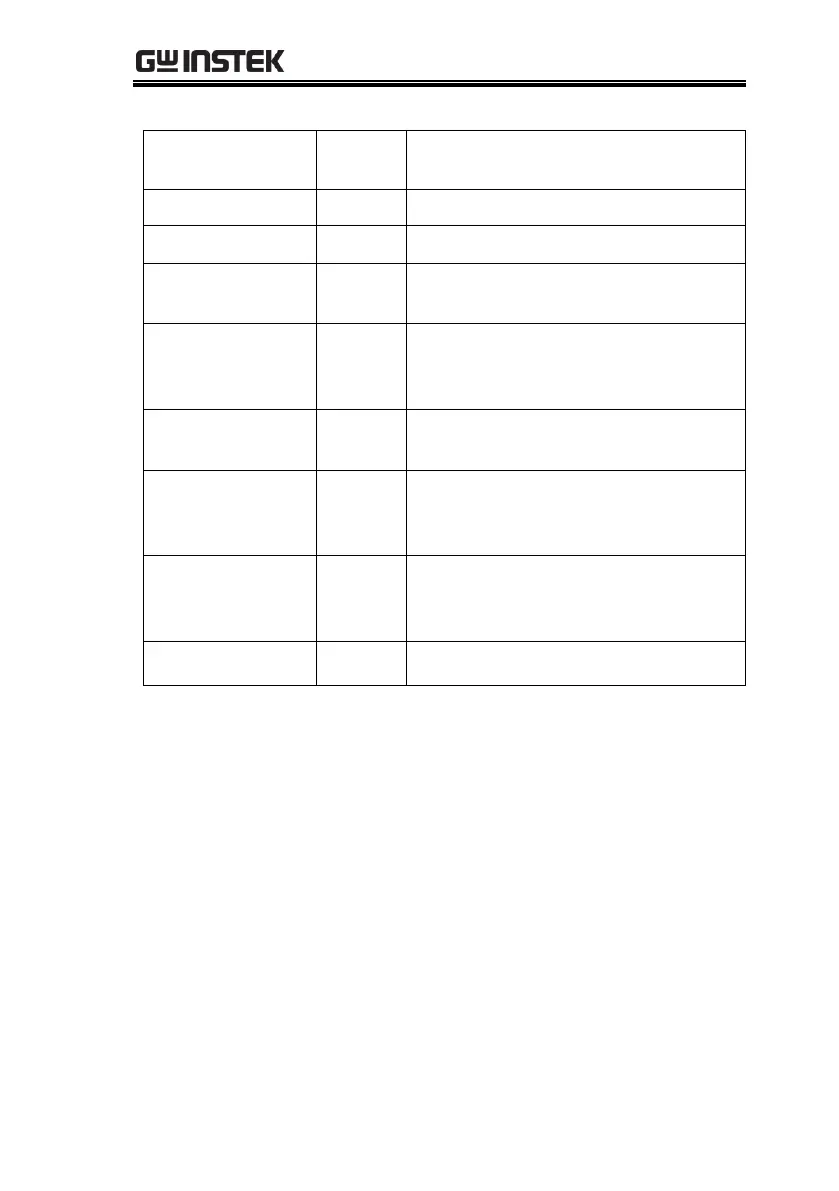

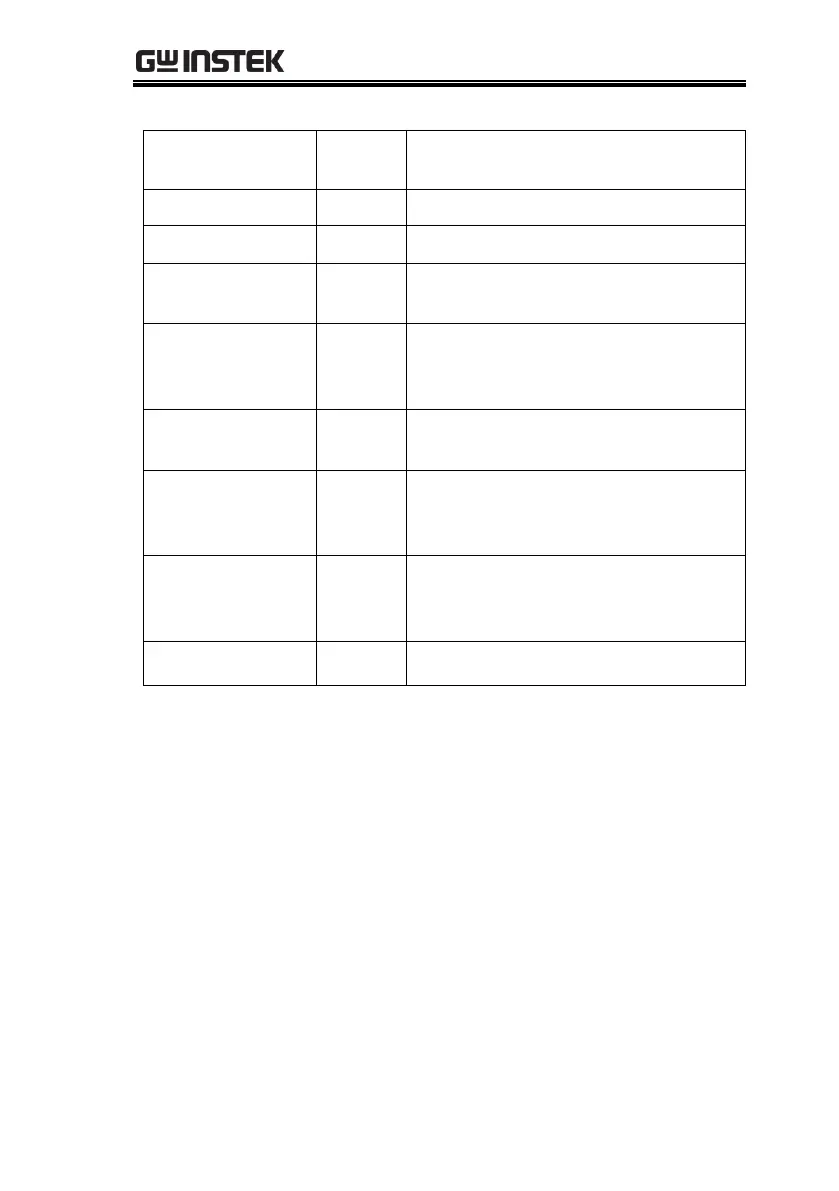

Bit Definition for the Status Byte Register

Indicates that one or more errors

are stored in the error queue.

3 Questionable

Summary bit

One or more bits are set in the

questionable data register (for

enabled events).

Indicates that a message is

available in the output queue.

5 Standard Event

Summary bit.

Indicates that one or more bits are

set in the standard event register.

(For enabled events).

Indicates that a summary bit is set

in the status byte register. (for

enabled summary bits)

The status byte condition register is cleared when one of the

following occurs:

*CLS command is used to clear the status byte register.

You read the event register from another register group (only

clear the corresponding bit in the condition register)

The status byte enable register is cleared when the following occurs:

When the *SRE 0 is command is executed.

Use the *STB? query to read the status byte register.

The *STB? query will return the contents of the status byte register

as long as the bit 6 (MSS) has been cleared.

Using the *OPC? query to place a signal in the output buffer.

Loading...

Loading...