128 IBM eX5 Implementation Guide

The MAX5 is connected to the x3690 X5 using two cables, connecting the QPI ports on the

server to two of the four QPI ports on the MAX5. The other two QPI ports of the MAX5 are

unused. The EXA ports are for future scaling capabilities.

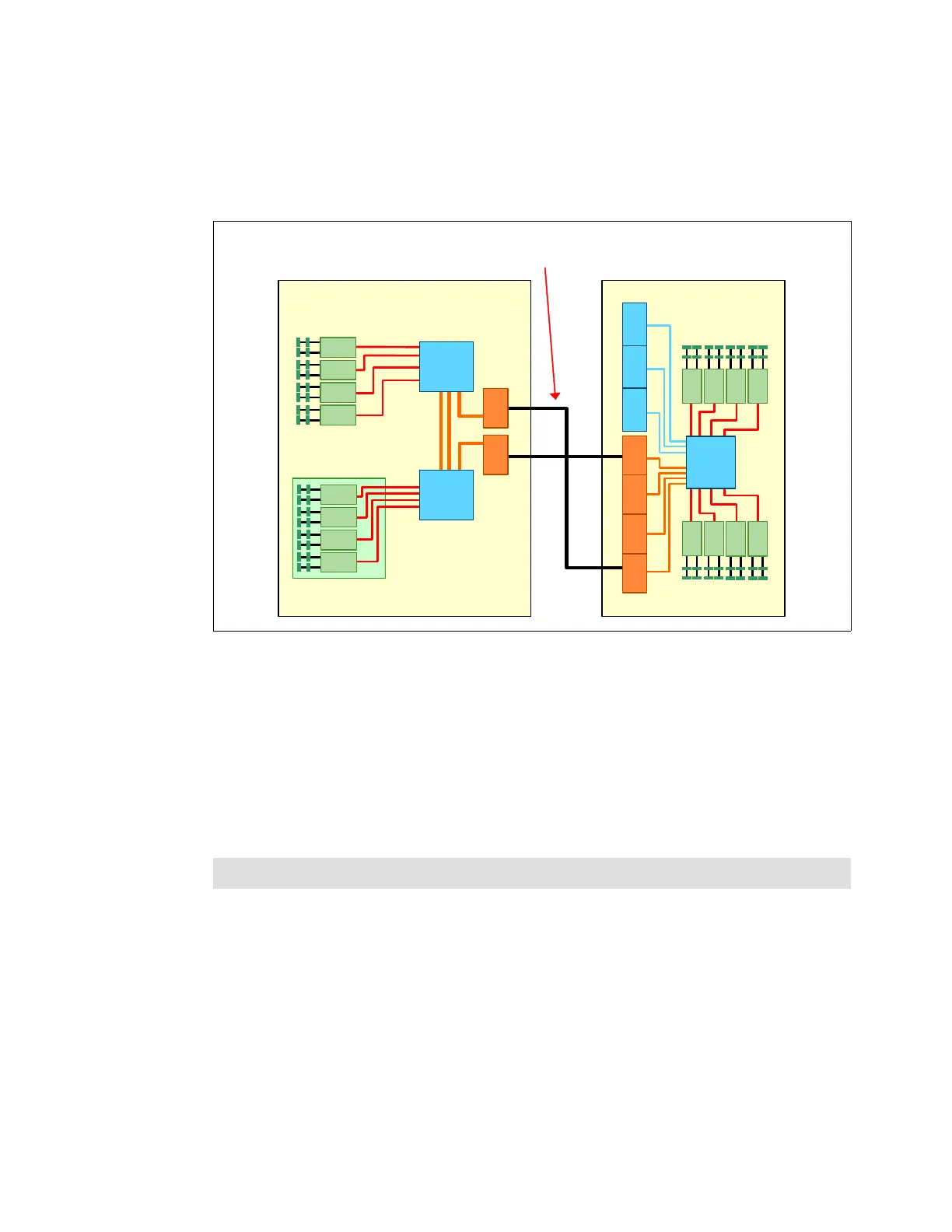

Figure 4-11 shows architecturally how a single-node x3690 X5 is connected to a MAX5.

Figure 4-11 Connectivity of the x3690 X5 with a MAX5 memory expansion unit

As shown in Figure 4-11, the x3690 X5 attaches to the MAX5 using QPI links; you can see

that the eX5 chip set in the MAX5 simultaneously connects to both CPUs in the server.

One benefit of this connectivity is that the MAX5 is able to store a copy of the contents of the

last-level cache of all the CPUs in the server. Therefore, when a CPU requests content stored

in the cache of another CPU, the MAX5 not only has that same data stored in its own cache,

it is able to return the acknowledgement of the snoop

and the data to the requesting CPU in

the same transaction. For more information about QPI links and snooping, see 2.2.4,

“QuickPath Interconnect (QPI)” on page 18.

Connectivity of the MAX5 to the x3690 X5 is described in 4.6, “Scalability” on page 128.

For memory configuration information, see 4.8.3, “MAX5 memory” on page 136. For a

description of the power and fans, see 4.12, “Power supplies” on page 173.

4.6 Scalability

In this section, we describe how the x3690 X5 can be expanded to increase the number of

memory DIMMs.

Tip: The Xeon E6510 processor does not support the use of the MAX5.

QPI

links

16 DIMMs on

system planar

Memory tray

(16 DIMMs)

SMI

links

CPU

0

CPU

1

MAX5

EXA

QPI

QPI

EXA

EXA EXAQPI

x3690 X5

QPIQPI

QPI

QPI

32 DIMMs

on MAX5

External

QPI cables

Loading...

Loading...