Chapter 3. IBM System x3850 X5 and x3950 X5 69

page 64, Also, you can order the MAX5 separately, as listed in Table 3-6. When ordering a

MAX5, remember to order the cable kit as well. For power supply fault redundancy, order the

optional power supply.

Table 3-6 Ordering information for the IBM MAX5 for System x

The eX5 chip set in the MAX5 is an IBM unique design that attaches to the QPI links as a

node controller, giving it direct access to all CPU bus transactions. It increases the number of

DIMMs supported in a system by a total of 32, and it also adds another 16 channels of

memory bandwidth, boosting overall throughput. Therefore, the MAX5 adds additional

memory and performance.

The eX5 chip connects directly through QPI links to all of the CPUs in the x3850 X5, and it

maintains a directory of each

CPU’s last-level cache. Therefore, when a CPU requests

content stored in the cache of another CPU, the MAX5 not only has that same data stored in

its own cache, it is able to return the acknowledgement of the snoop

and the data to the

requesting CPU in the same transaction. For more information about QPI links and snooping,

see 2.2.4, “QuickPath Interconnect (QPI)” on page 18.

The MAX5 also has EXA scalability ports used in an EXA-scaled configuration (that is, a

2-node and MAX5 configuration). These ports are reserved for future use.

In summary, the MAX5 offers the following major features:

Adds 32 DIMM slots to either the x3850 X5 or the x3690 X5

Adds 16 channels of memory bandwidth

Improves snoop latencies

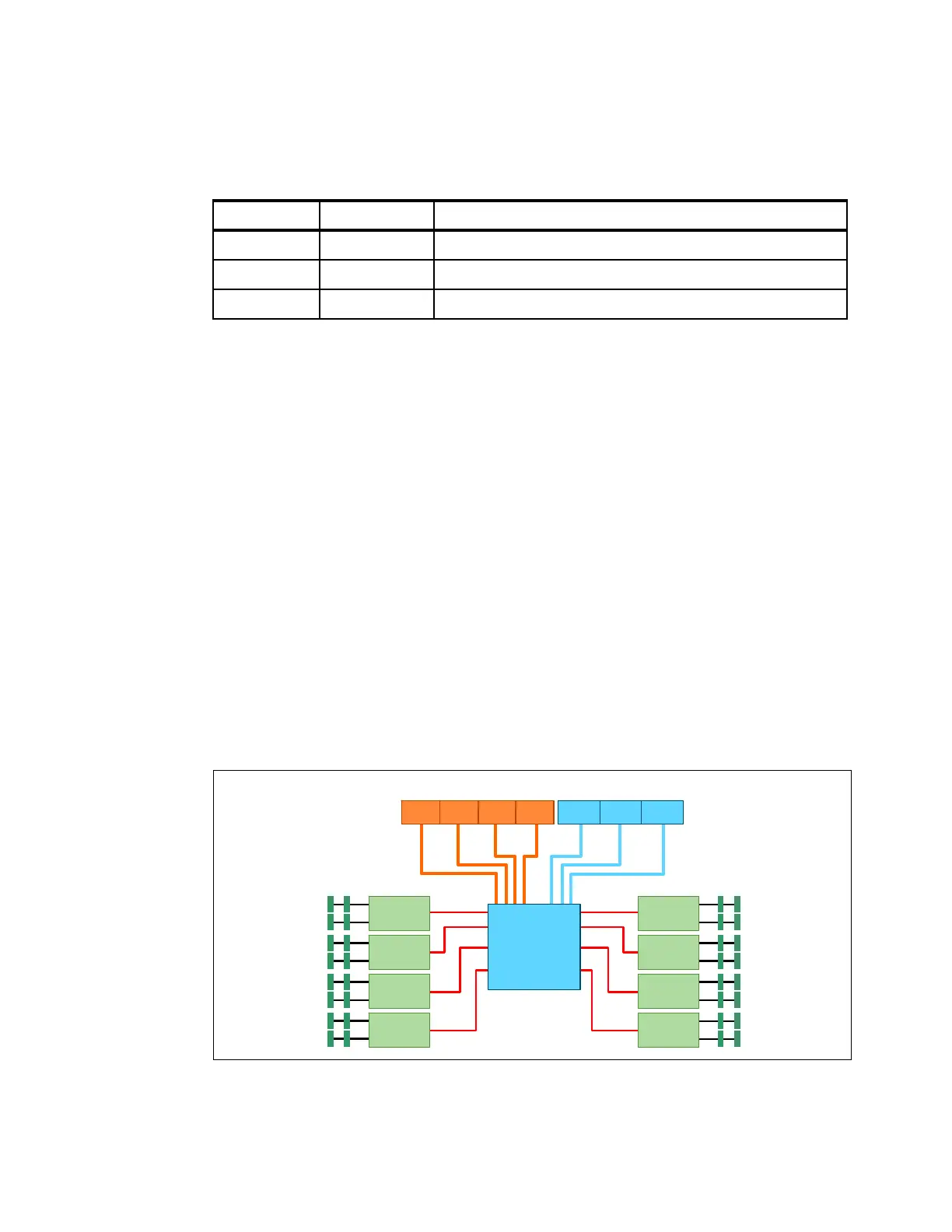

Figure 3-11 shows a diagram of the MAX5.

Figure 3-11 MAX5 block diagram

Part number Feature code Description

59Y6265 4199 IBM MAX5 for System x

60Y0332 4782 IBM 675W HE Redundant Power Supply

59Y6267 4192 IBM MAX5 to x3850 X5 Cable Kit

SMI

links

DDR3 DIMMs

(Two DIMMs per channel)

Memory

buffer

Memory

buffer

Memory

buffer

Memory

buffer

SMI

links

Memory

buffer

Memory

buffer

Memory

buffer

Memory

buffer

DDR3 DIMMs

(Two DIMMs per channel)

External connectors

QPI QPIQPI QPI EXA EXA EXA

IBM EXA

chip

QPI QPI

Loading...

Loading...