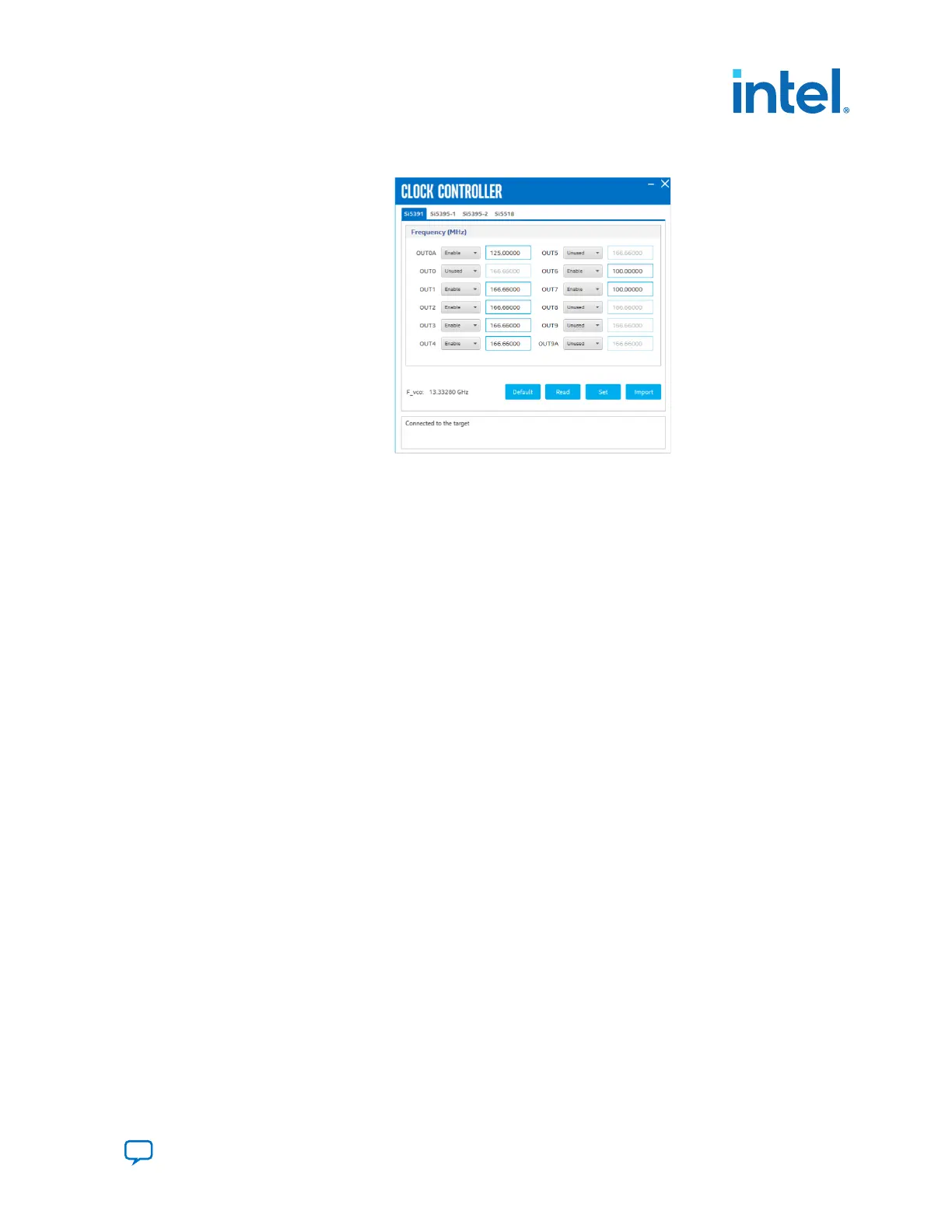

Figure 22. Si5391

The following sections describe the Clock Controller buttons.

Read

Reads the current frequency setting for the oscillator associated with the active tab.

Default

Sets the frequency for the oscillator associated with the active tab back to its default

value. This can also be accomplished by power cycling the board.

Set

Sets the programmable oscillator frequency for the selected clock to the value in the

OUTx output controls for Si5391. Frequency changes might take several milliseconds

to take effect. You might see glitches on the clock during this time. Intel recommends

resetting the FPGA logic after changing frequencies.

Import

Si5391 has a two-time rewritable non-volatile memory (NVM). You can generate the

register list from the Clockbuilder Pro tool and import it into Si5391 to update the

settings of the RAM. Register changes are volatile after power cycling.

4. Board Test System

776646 | 2023.05.31

Send Feedback

Intel Agilex

®

7 FPGA I-Series Transceiver (6 × F-Tile) Development Kit User

Guide

25

Loading...

Loading...