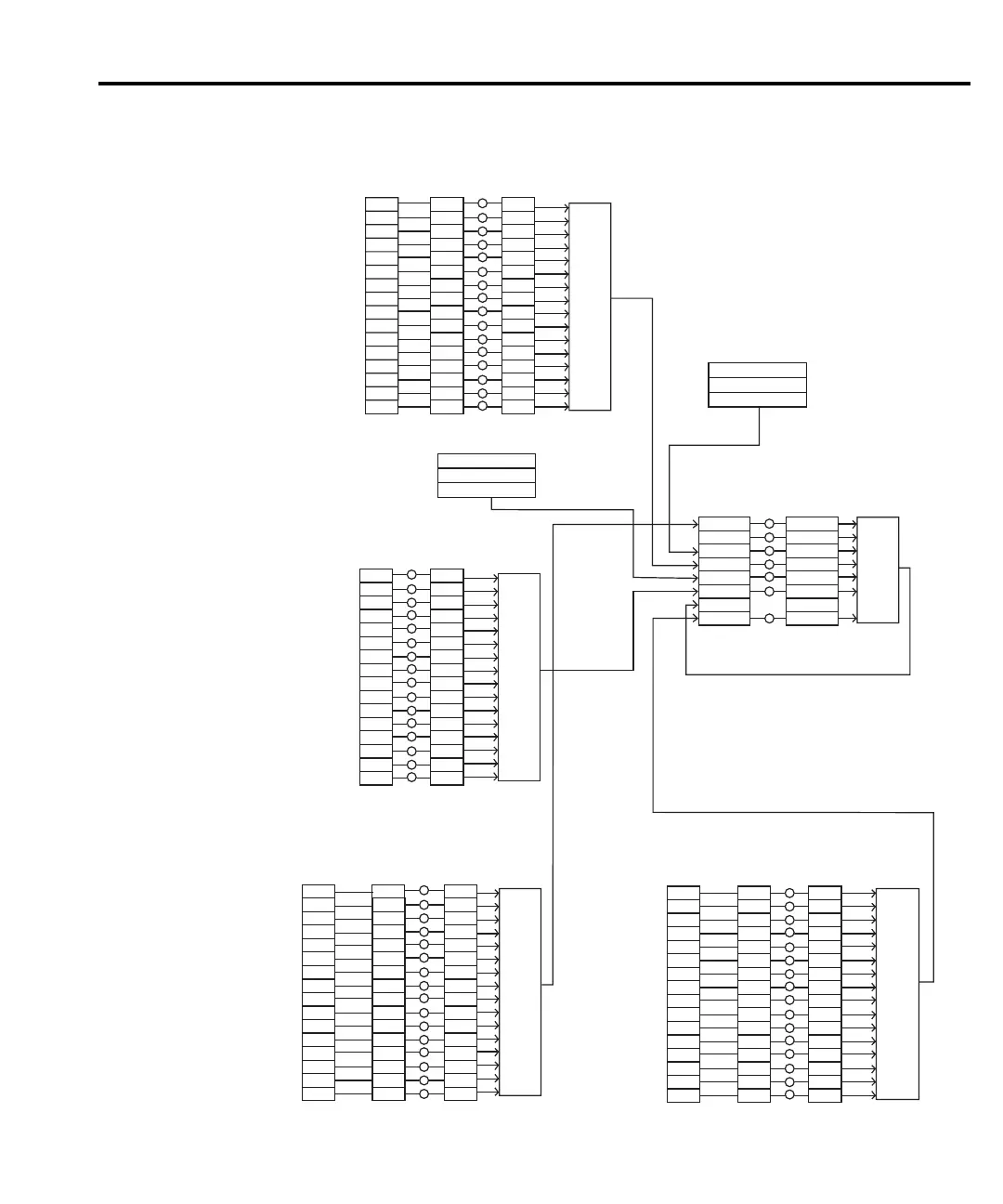

3

5

6

Cal

9

10

11

12

13

14

15

Condition

Register

(Always Zero)

3

5

6

9

10

11

12

13

15

Event

Register

3

5

6

9

10

11

12

13

15

Event

Enable

Register

&

&

&

&

&

&

&

&

&

&

&

&

&

&

&

&

Logical

OR

11

12

13

15

Condition

Register

Event

Register

Event

Enable

Register

&

&

&

&

&

&

&

&

&

&

&

&

&

&

&

&

Logical

OR

EAV

QSB

MAV

ESB

RQS/MSS

OSB

Status

Byte

Register

1

EAV

QSB

MAV

ESB

6

OSB

Service

Request

Enable

Register

&

&

&

&

&

&

&

Logical

OR

*STB?

*SRE

*SRE?

Master Summary Status (MSS)

MSB = Measurement Summary Bit

EAV = Error Available

QSB = Questionable Summary Bit

MAV = Message Available

ESB = Event Summary Bit

RQS/MSS = Request for Service/Master Summary Staus

OSB = Operation Summary Bit

Error Queue

Output Queue

Note : RQS bit is in serial poll byte,

MSS bit is in *STB? response.

1

14 14

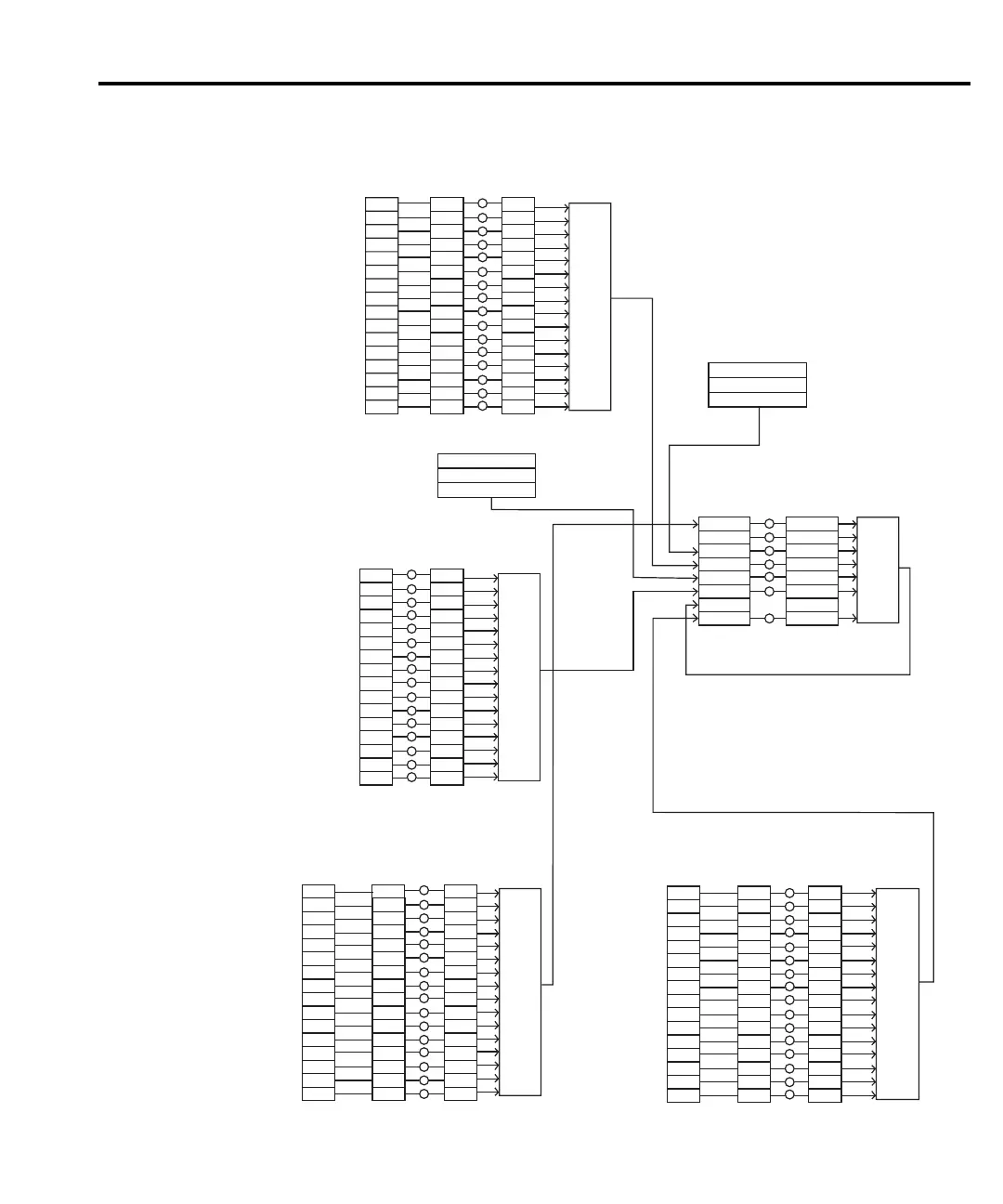

OPC

QYE

DDE

EXE

CME

URQ

PON

8

9

11

12

13

15

Register

8

9

11

12

13

15

Register

&

&

&

&

&

&

&

&

&

&

&

&

&

&

&

&

Logical

OR

(Always Zero)

Operation Complete

Query Error

Device Specific Error

Execution Error

Command Error

User Request

Power On

OPC

QYE

DDE

EXE

CME

URQ

PON

*ESR?

*ESE?

MSB MSB

12

13

14

15

(Always Zero)

Event

Register

Event

Enable

Register

&

&

&

&

&

&

&

&

&

&

&

&

&

&

&

&

Logical

OR

Condition

Register

11

Calibration Summary

0

9

11

4

4

4

0

1

2

0

1

2

0

1

2

7

14

:CONDition?

[:EVENt]? :ENABle <NRf>

:ENABle?

Questionable Event Registers

14

14

10

10

*ESE <NRf>

Event

Event Enable

Standard Event Registers

BF1

Pulse Trigger Timeout Channel 1

PTT1

Reading Overflow Channel 1

ROF1

2

1

0

:CONDition?

[:EVENt]?

:ENABle <NRf>

:ENABle?

CL1

CLT1

PSS

10

Current Limit Tripped 1

Power Supply Shutdown

(Always Zero)

VPT1

Current Limit 1

:CONDition? [:EVENt]?

:ENABle <NRf>

:ENABle?

Operation Event Registers

Cal

7

Cal

7

Measurement Event Registers

12

13

14

15

11

2

1

0

12

13

14

15

11

2

1

0

14

11

12

13

15

0

9

PSS

10

14

11

12

13

15

0

9

PSS

10

VPT Channel 1

VPT Channel 2

VPT2

Heat Sink Shutdown

Current Limit 2

Reading

Available Channel 1

Reading Overflow Channel 2

Reading Available Channel 2

Buffer Full Channel 1

Buffer Full Channel 2

RAV1

BF2

PTT2

ROF2

RAV2

Pulse Trigger Timeout Channel 2

BF1

PTT1

ROF1

RAV1

BF2

PTT2

ROF2

RAV2

BF1

PTT1

ROF1

RAV1

BF2

PTT2

ROF2

RAV2

CL2

VPT1

VPT2

VPT1

VPT2

CL1

CL1

CLT1

CLT1

HSS

HSS

HSS

CL2 CL2

Current Limit Tripped 2 CLT2 CLT2 CLT2

Figure 8-1

Status model structure

Status Structure 8-3

Test Equipment Depot - 800.517.8431 - 99 Washington Street Melrose, MA 02176

TestEquipmentDepot.com

Loading...

Loading...