XGB Analog edition manual

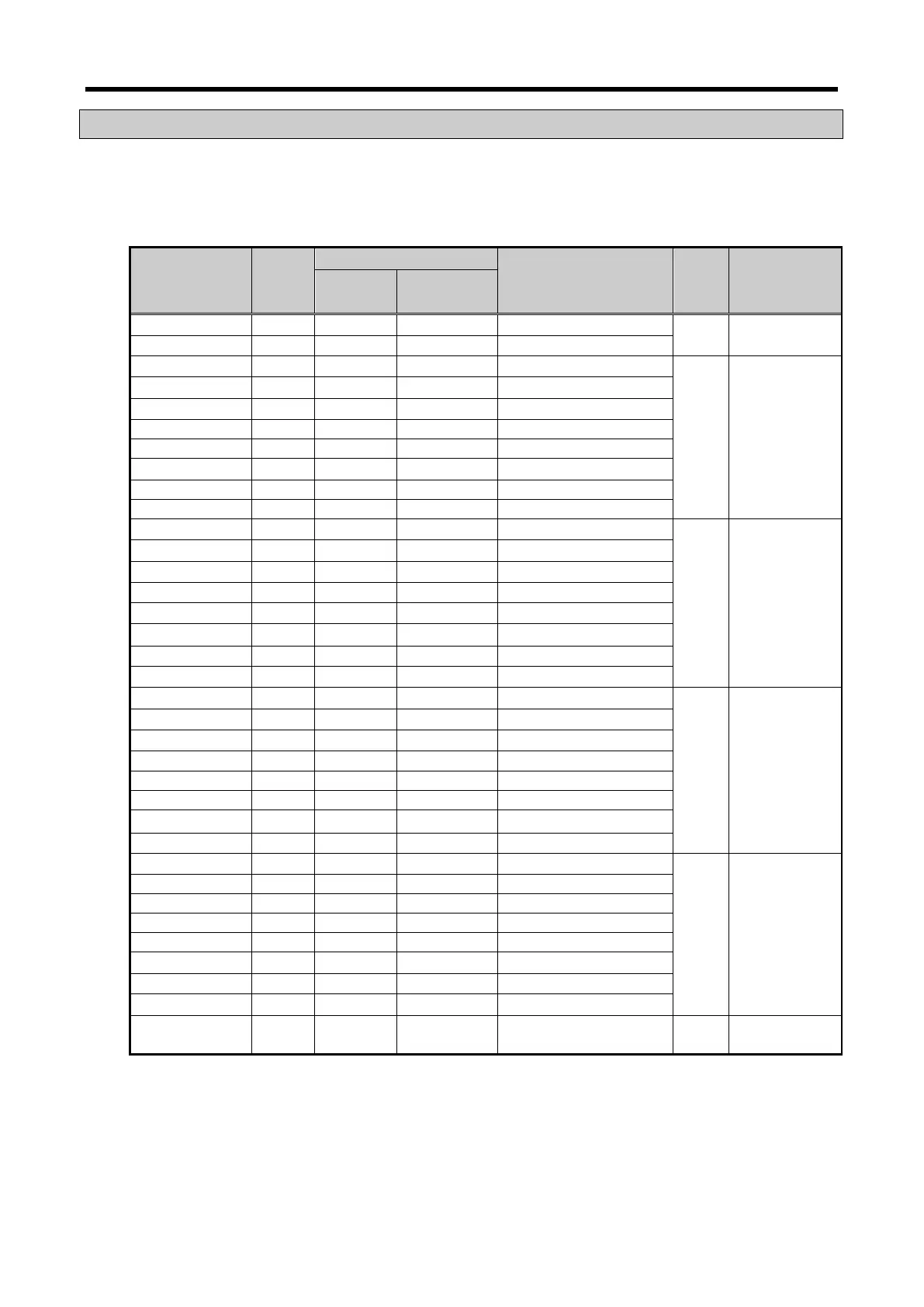

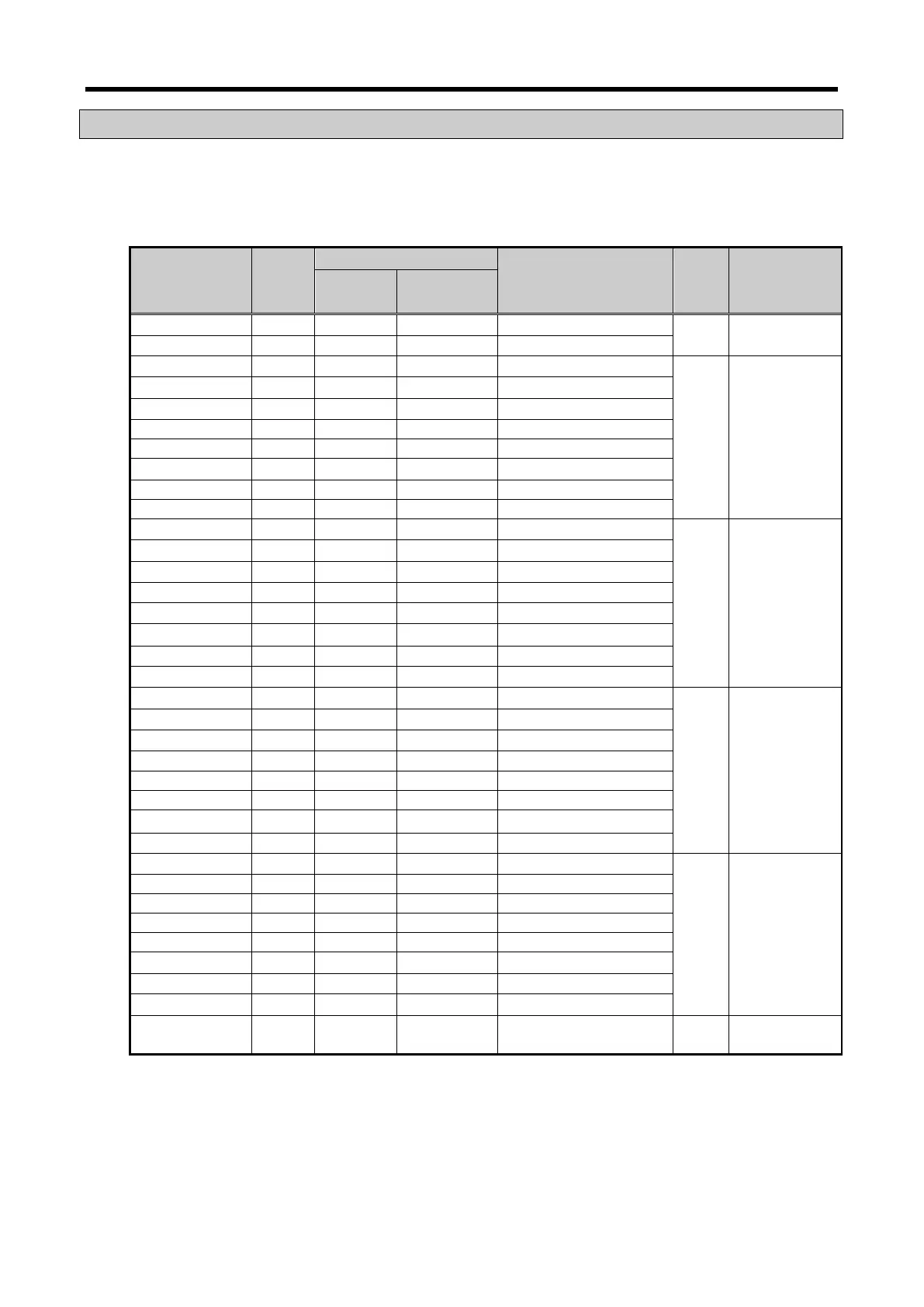

7.11 Configuration and Function of Internal Memory

An analog mix module has internal memory for data communication with XGB base unit.

7.11.1 Analog Data I/O Area

The table below presents the analog data I/O area.

Variable Type

Description

Read/

Write

Signal

direction

“S”or

“H”type

IEC type

Read AD08A → CPU

Read AD08A → CPU

Read AD08A → CPU

Read AD08A → CPU

_0y_CH6_DATA WORD

U0y.08

%UW0.y.8

CH6 Output

Read AD08A → CPU

_0y_CH7_IDD BIT U0y.10.7 %UX0.y.167 CH7 Disconnection flag

_0y_ERR_CLR BIT U0y.11.0 %UX0.y.176 Error Clear Request

Read/

AD08A ↔ CPU

7 - 28

Loading...

Loading...