b6,

TIM Timer Interrupt Mask -

Used

to inhibit the timer interrupt

to

the processor when

it

is

a

logic one.

1 =

Set by

an

external reset or under program control.

0=

Cleared under program control.

b5,

TIN External or Internal - Selects the input clock source to

be

either the external TIMER (pin

8)

or the internal phase two.

1 =

Selects the external clock source.

0=

Selects the internal phase

two

(fOSC+4) clock source.

b4,

TIE

External Enable - Used

to

enable the external TIMER (pin

8)

or

to

enable the internal

clock

(if TIN =

0)

regardless of the external TIMER pin state (disables gated clock feature).

When

TOPT =

1,

TIE

is

always a logic one.

1 =

Enables

external TIMER pin.

0=

Disables external TIMER pin.

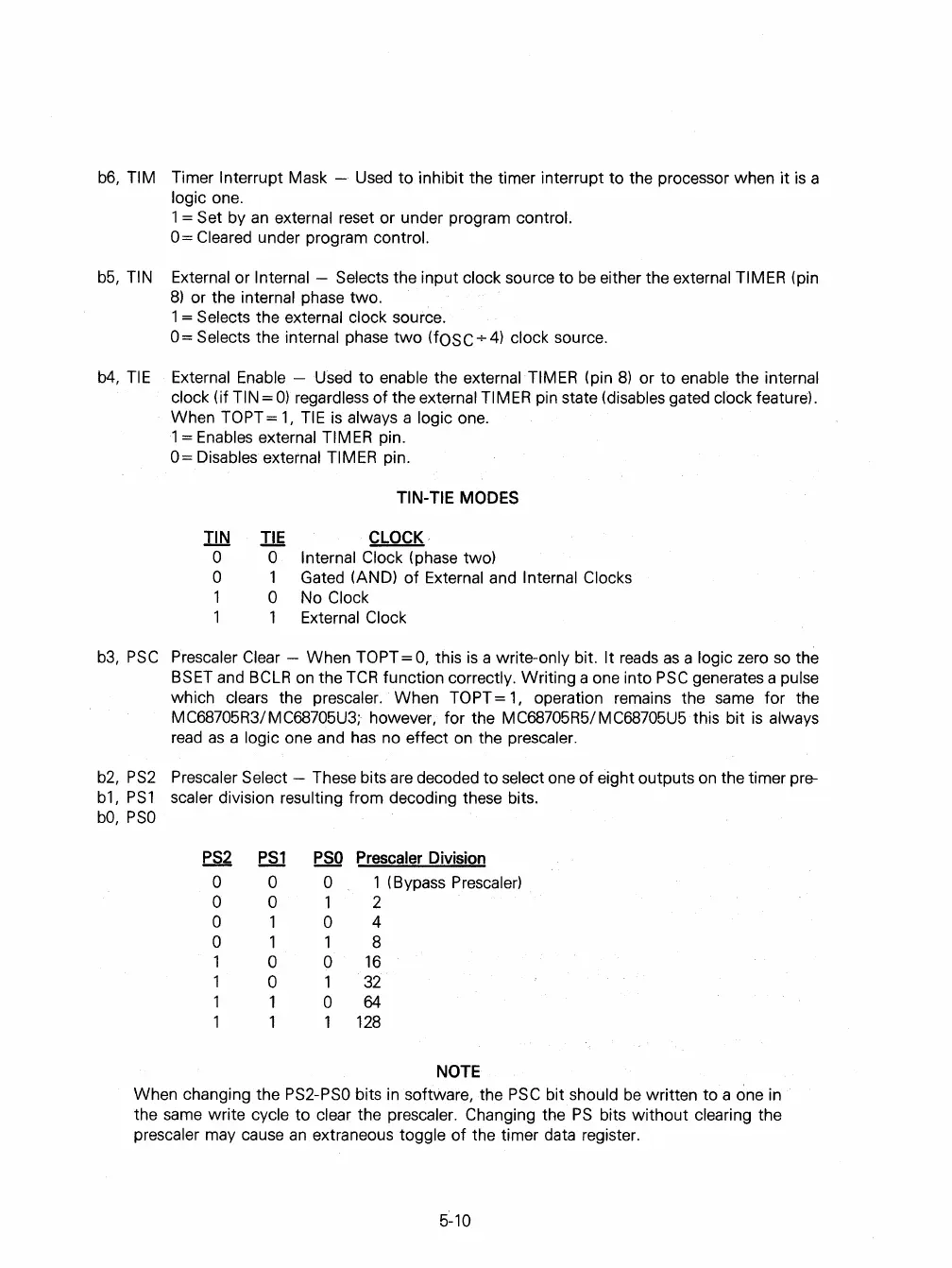

TIN-TIE

MODES

TIN

TIE

CLOCK

a a Internal Clock (phase two)

a 1 Gated (AND)

of

External and Internal Clocks

1 a No Clock

1 1 External Clock

b3,

PSC

Prescaler Clear - When TOPT =

a,

this

is

a write-only bit. It

reads

as

a logic zero

so

the

BSET

and

BCLR

on

the

TCR

function correctly. Writing a one into

PSC

generates a pulse

which clears the prescaler. When TOPT =

1,

operation remains the same for the

MC68705R3/MC68705U3; however, for the MC68705R5/MC68705U5 this bit

is

always

read

as

a logic one and

has

no effect

on

the prescaler.

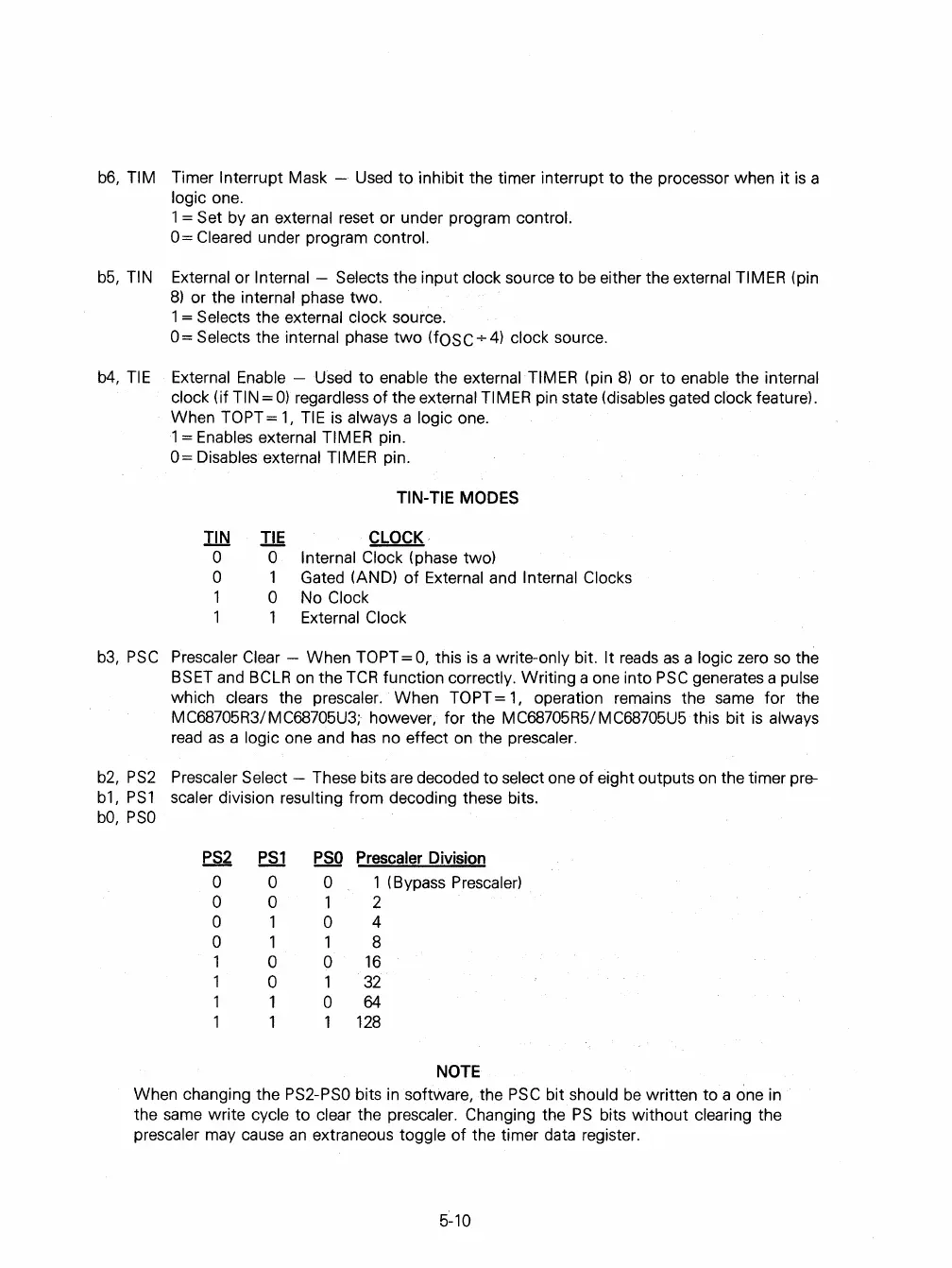

b2,

PS2

Prescaler Select - These bits

are

decoded to select one of eight outputs

on

the timer pre-

bl,

PSl scaler division resulting from decoding these bits.

bO,

PSO

PS2

PSl

PSO

Prescaler

Division

a

a

a

1 (Bypass Prescaler)

a a

1

2

a

1

a

4

a

1 1 8

1

a a

16

1

a 1

32

1

1

a

64

1

1 1

128

NOTE

When changing the

PS2-PSO

bits

in

software, the

PSC

bit should

be

written to a one

in

the

same

write cycle to clear the prescaler. Changing the

PS

bits without clearing the

prescaler may cause

an

extraneous toggle of the timer data register.

5-10

Loading...

Loading...