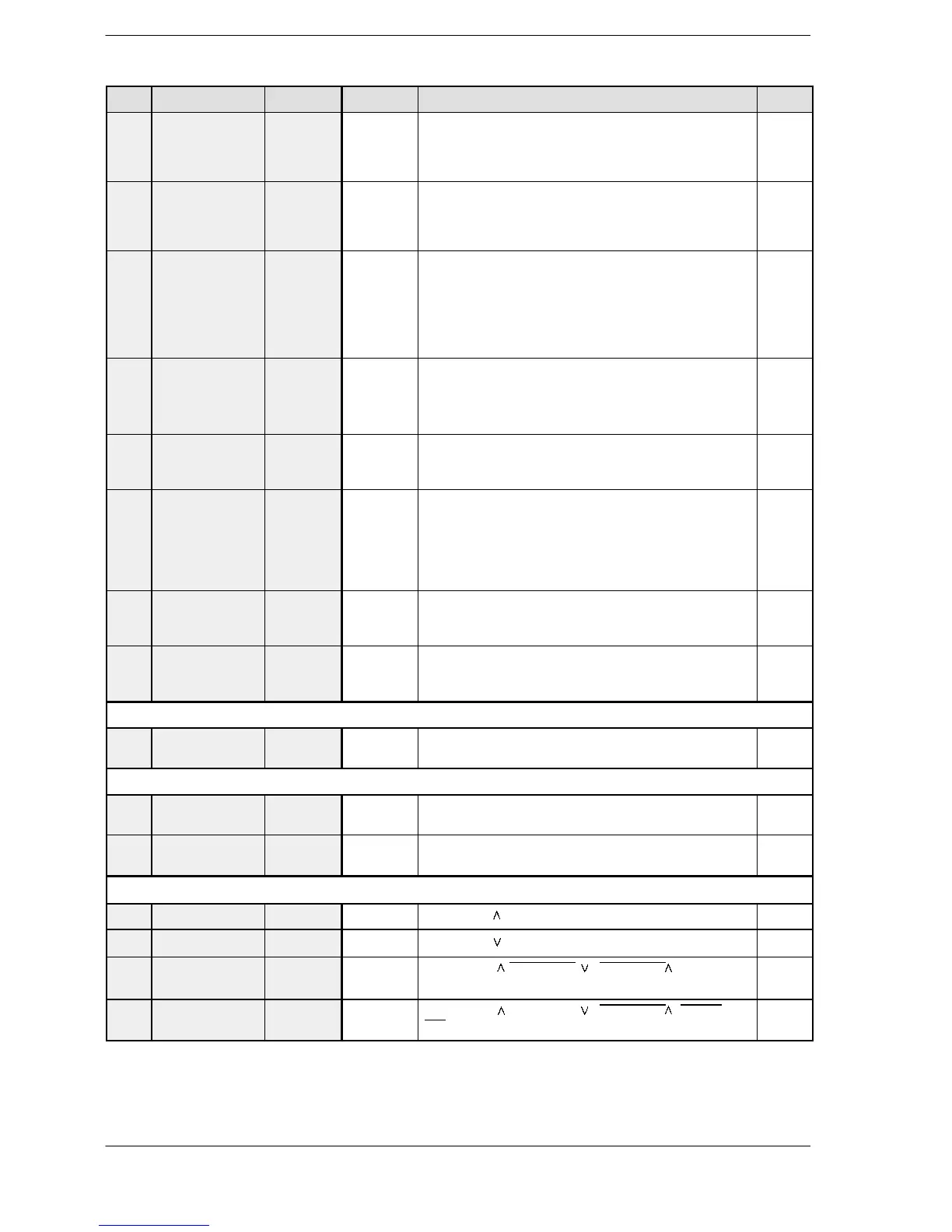

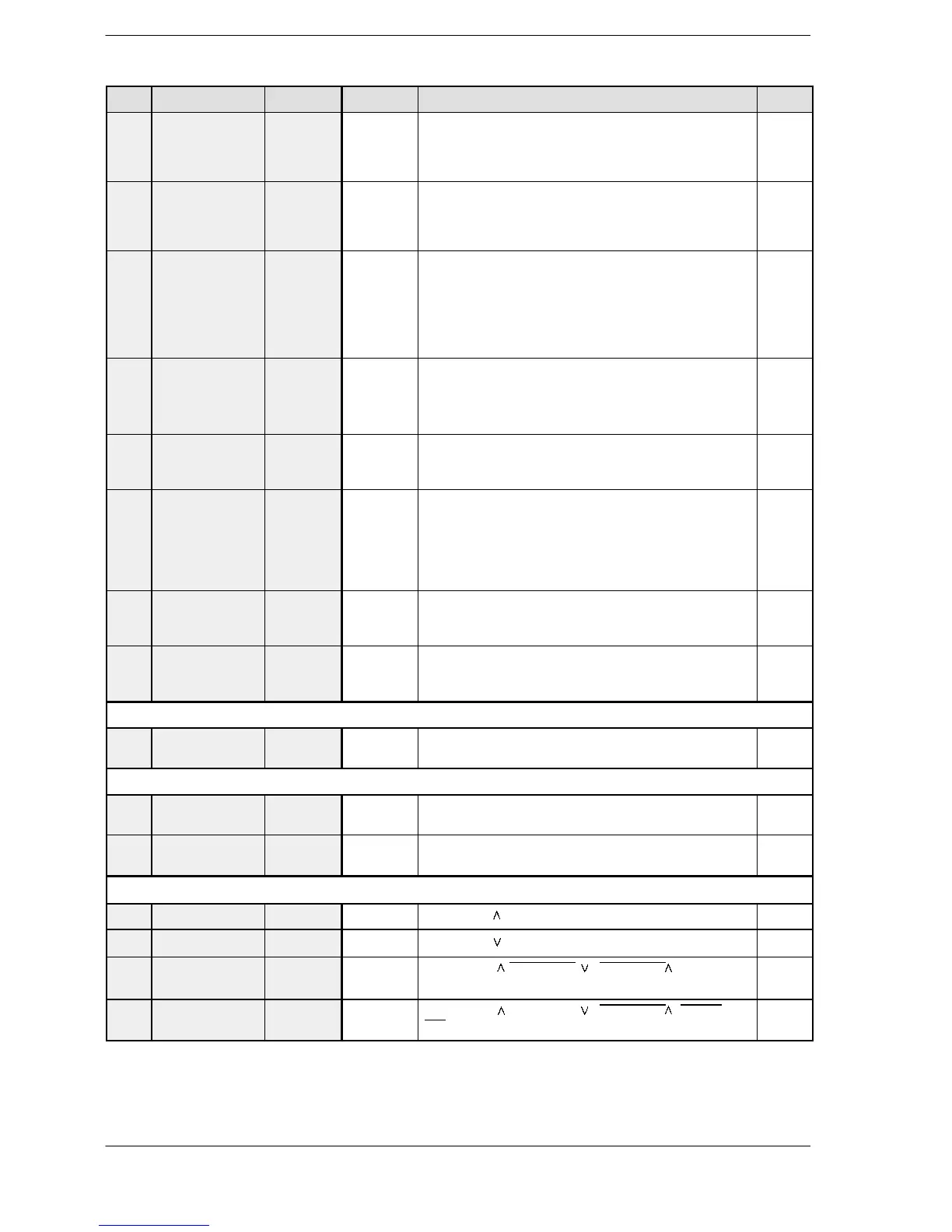

FPΣ

13.8 Table of Instructions

13 - 59

No. Name Boolean Operand Description Steps

F166 Target value

much on

(with channel

specification)

HC1S n, S, D Turns output Yn on when the elapsed value of the

built-in high-speed counter reaches the target value of

(S+1,S).

11

F167 Target value

much off

(with channel

specification)

HC1R n, S, D Turns output Yn off when the elapsed value of the

built-in high-speed counterreaches the target value of

(S+1,S).

11

F171 Pulse output

(with channel

specification)

(Trapezoidal

control and

home return)

SPDH S, n Positioning pulses are output from the specified chan-

nel, in accordance with the contents of the data table

that starts with S.

5

F172 Pulse output

(with channel

specification)

(JOGoperation)

PLSH S, n Pulse strings are output from the specified output, in

accordance with the contents of the data table that

starts with S.

5

F173 PWM output

(with channel

specification)

PWMH S, n PWM output is output from the specified output, in ac-

cordance with the contents of the data table that starts

with S.

5

F174 Pulse output

(with channel

specification)

(Selectable

data table con-

trol operation)

SP0H S, n Outputs the pulses from the specified channel accord-

ing to the data table specified by S.

5

F175 Pulse output

(Linear inter-

polation)

SPSH S, n Pulses are output from channel, in accordance withthe

designated data table, so that the path to the target

position forms a straight line.

5

F176 Pulse output

(Circular

interpolation)

SPCH S, n Pulses are output from channel, in accordance with the

designated data table, so that the path to the target

position forms an arc.

5

Basic function instruction

F183 Auxiliary timer

(32-bit)

DSTM S, D Turn on the specified output and R900D after set value

“S” × 0.01 sec..

7

Data transfer instructions

F190 Three 16-bit

data move

MV3 S1, S2,

S3, D

(S1) → (D), (S2) → (D+1), (S3) → (D+2) 10

F191 Three 32-bit

data move

DMV3 S1, S2,

S3, D

(S1+1, S1) → (D+1, D), (S2+1, S2) → (D+3, D+2),

(S3+1, S3) → (D+5, D+4)

16

Logic operation instructions

F215 32-bit data AND DAND S1, S2, D

(S1+1, S1) (S2+1, S2) → (D+1, D)

12

F216 32-bit data OR DOR S1, S2, D

(S1+1, S1) (S2+1, S2) → (D+1, D)

12

F217 32-bit data XOR DXOR S1, S2, D

{(S1+1, S1) (S2+1, S2)} {(S1+1, S1) (S2+1, S2)}

→ (D+1, D)

12

F218 32-bit data XNR DXNR S1, S2, D

{(S1+1, S1) (S2+1, S2)} {(S1+1, S1) (S2+1,

S2)

} → (D+1, D)

12

Loading...

Loading...