USB and PCIe

PRELIMINARY INFORMATION

NVIDIA Jetson Orin NX DG-10931-001_v0.1 | 24

7.1.1 USB 2.0 Design Guidelines

The following table details the requirements that apply to the USB 2.0 controller PHY

interfaces:

USB[2:0]_D_N/P.

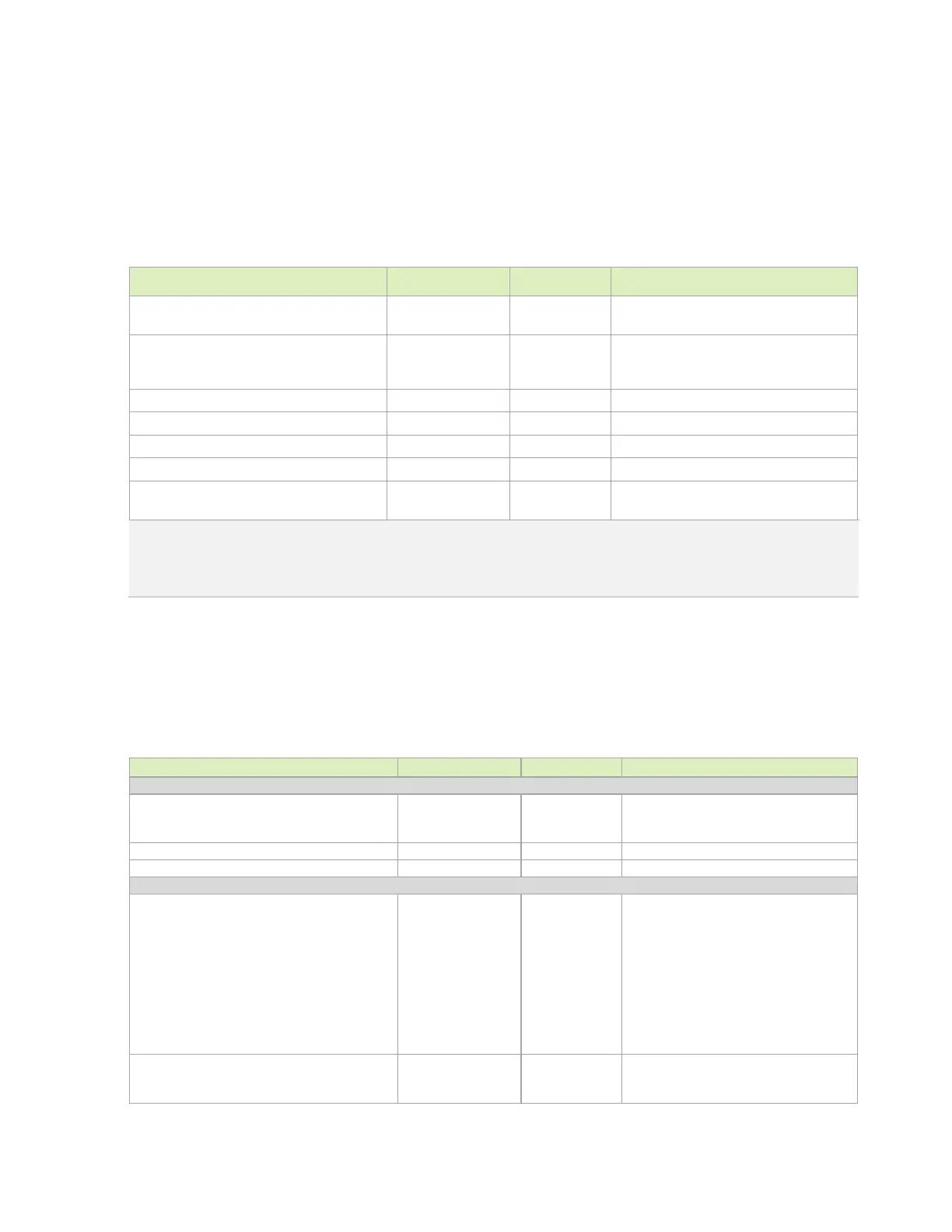

Table 7-4. USB 2.0 Interface Signal Routing Requirements

Max frequency (high speed): Bit Rate/UI

period/Frequency

480/2.083/240 Mbps/ns/MHz

Max loading: High Speed / Full Speed / Low

Speed

10 / 150 / 600 pF Max loading should include any passive

and active components on the trace such

as CMC, Switch, ESD etc.

Reference plane GND

Trace impedance: Diff pair / SE) 90 / 50 Ω ±15%

Via proximity (signal to reference) < 3.8 (24) mm (ps) See Note 1

Max trace length/delay 6 (960) In (ps)

Max intra-pair skew between

and

7.5 ps

Notes:

1. Up to four signal vias can share a single GND return via.

2. Adjustments to the USB drive strength, slew rate, termination value settings should not be necessary, but if any are made, they

MUST be done as an offset to default values instead of overwriting those values.

7.1.2 USB 3.2 Design Guidelines

The following table details the requirements that apply to the USB 3.2 PHY interfaces.

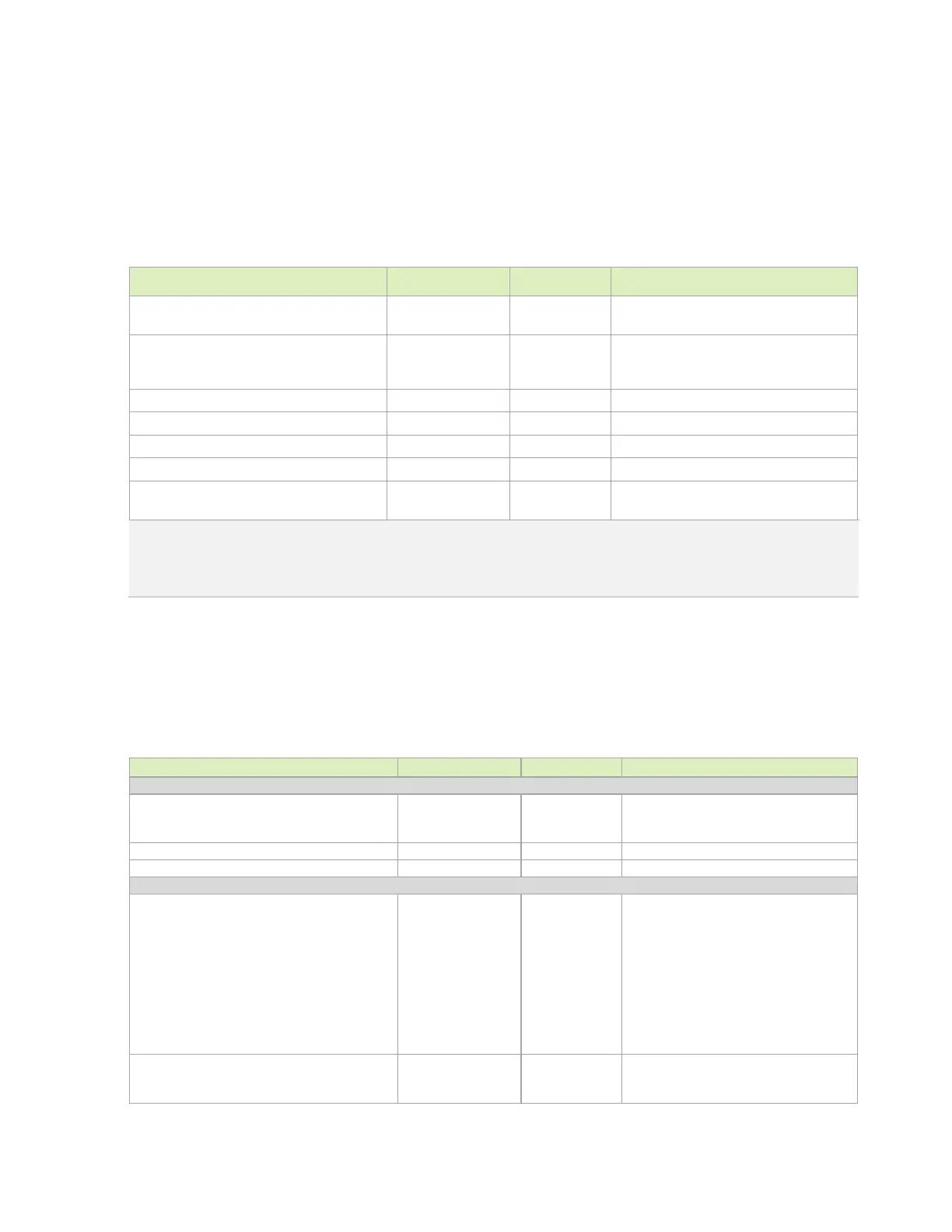

Table 7-5. USB 3.2 Interface Signal Routing Requirements

Gen1

5.0 / 200

Gbps / ps

Device mode supports Gen1 speed only.

On-die termination at TX and RX

Gen1 Host (Type C)

Gen1 Host (Type A)

Gen1 Device (Type C)

Gen1 Device (Micro AB)

Gen2 (Dual role mode)

Resonance Dip Frequency

≥ -3.8

≥ -7.3

≥ -3.8

≥ -2.5 [*]

≥ -4.5

> 8

dB @ 2.5GHz

dB @ 2.5GHz

dB @ 2,5GHz

dB @ 2.5GHz

dB @ 5GHz

GHz

Only the PCB (and connector) without

added-on components such as CMC,

ESD, and Mux, is considered. The

connector is included. For Gen2 the

loss budget is the same for all

connector types. For dual role mode,

host and device have the same loss

budget

[*] the consideration of Gen1 fixture

Time-domain Reflectometer (TDR) Dip

Gen1

75

Ω

@ Tr = 61ps (10%-90%)

Loading...

Loading...