USB and PCIe

PRELIMINARY INFORMATION

NVIDIA Jetson Orin NX DG-10931-001_v0.1 | 35

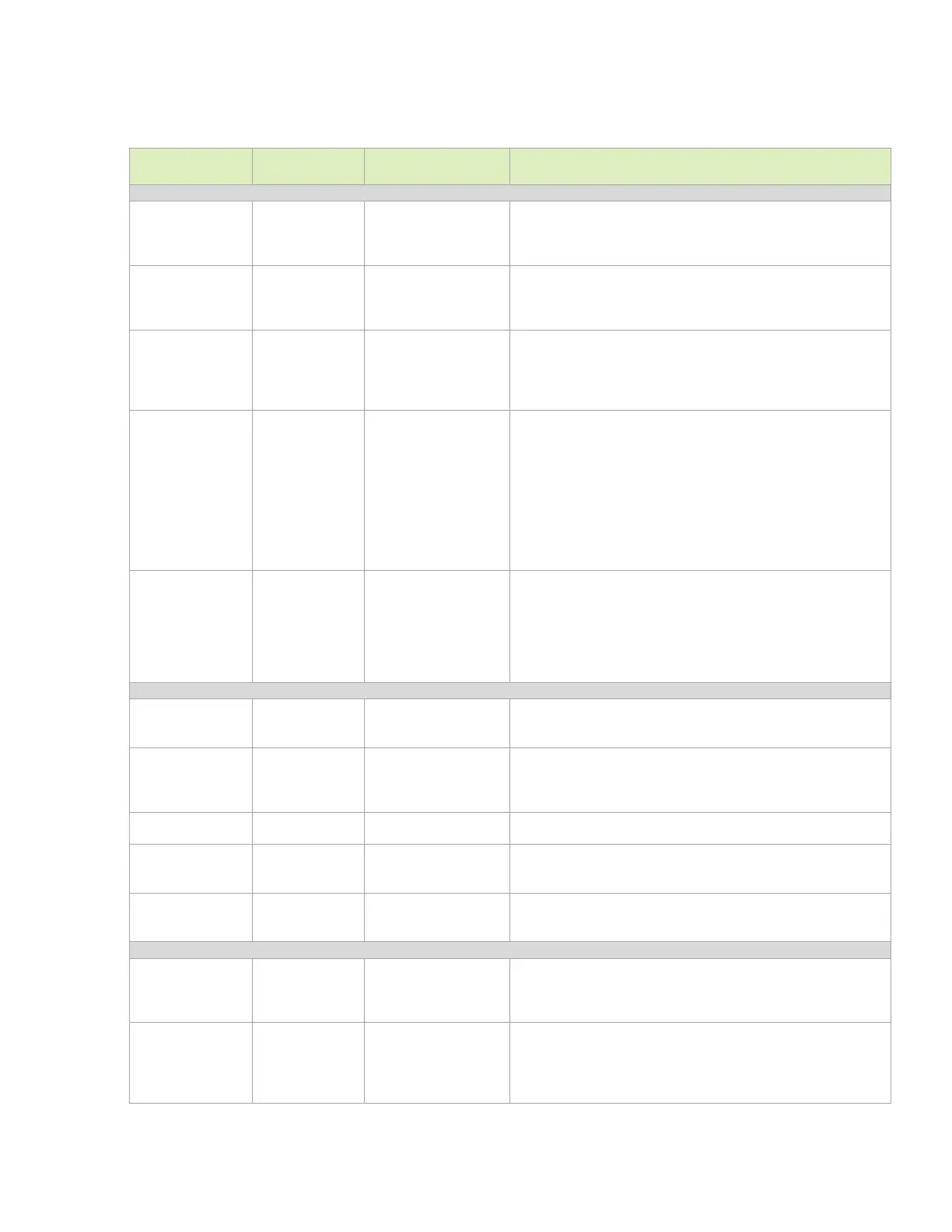

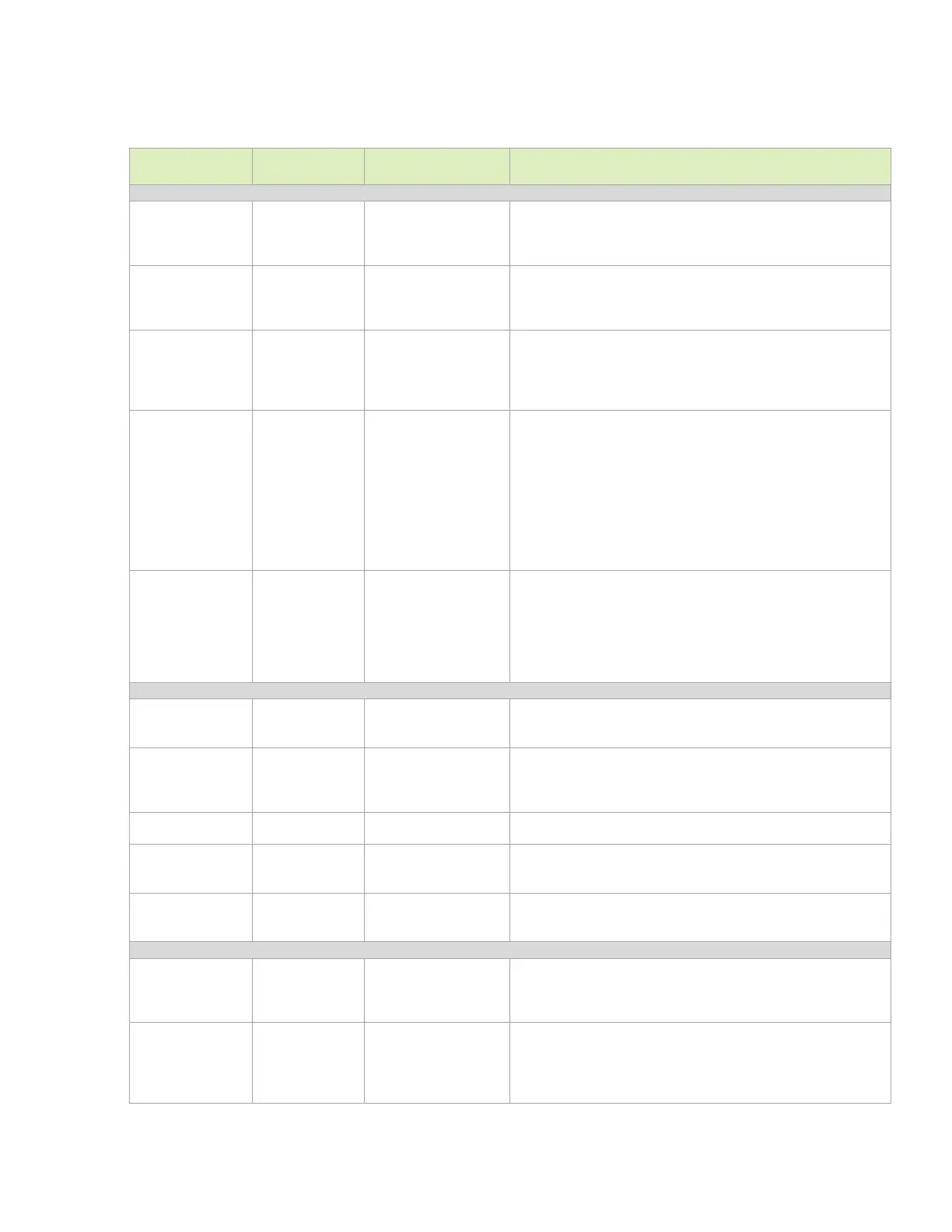

Table 7-10. PCIe Signal Connections

Module Pin

Name (Function)

PCIe Interface 0 (x4 – Controller #4, Root Port or Endpoint)

PCIE0_TX2_N/P

PCIE0_TX1_N/P

Capacitor

Differential Transmit Data Pairs: Connect to TX_N/P pins of PCIe

connector or RX_N/P pin of PCIe device through AC cap according

to supported configuration.

PCIE0_RX2_N/P

PCIE0_RX1_N/P

capacitors near Jetson

Orin NX pins or device

Differential Receive Data Pairs: Connect to RX_N/P pins of PCIe

connector or TX_N/P pin of PCIe device through AC cap according

to supported configuration.

Root Port

Endpoint

DIFF OUT

DIFF IN

Differential Reference Clock Output: Connected to a mux on the

module that selects either SF_PCIE10_CLK or UPHY2_REFCLK2.

Connect to REFCLK_N/P pins of PCIe device/connector. For Root

Port operation, set the mux to select SF_PCIE10_CLK (GP21 = 0).

For Endpoint, set the mux to select UPHY2_REFCLK2 (GP21 = 1).

Root Port

Endpoint

I

O

47kΩ pull-up to

VDD_3V3_SYS

on

module

PCIe Clock Request for PCIE0_CLK: Connect to CLKREQ pins on

device or connectors. If the module is configured as an Endpoint,

include isolation between the clock request pin on the module and

the device/connector. One isolator should have the output to the

module and be powered by the 3.3V rail on the module. The other

isolator should have the output pointing at the connector or device

and be powered by the 3.3V rail at the connector or device. These

isolate the on-module pull-up resistors as well as ensures the

pins on both the Root Port and Endpoint sides will not be driven

high before the associated power is enabled.

Root Port

Endpoint

O

I

4.7kΩ pull-up to

VDD_3V3_SYS

on

module

PCIe Reset: Connect to PERST pins on device/connector(s). If the

module is configured as an Endpoint, include a isolator between

the reset pin on the module and the device/connector powered by

the 3.3V rail at the connector or device. The isolator should have

the output toward the module. This isolates the on-module pull-up

resistor as well as ensures this signal will not be pulled or driven

high before the module is powered on.

PCIe Interface 1 (x1 – Controller #1, Root Port only)

Capacitor

Differential Transmit Data Pair: Connect to TX_N/P pins of PCIe

connector or RX_N/P pin of PCIe device through AC cap according

to supported configuration.

capacitors near Jetson

Orin NX pins or device

Differential Receive Data Pair: Connect to RX_N/P pins of PCIe

connector or TX_N/P pin of PCIe device through AC cap according

to supported configuration.

Differential Reference Clock Output: Connect to REFCLK_N/P

pins of PCIe device/connector

I (Endpoint)

47kΩ pull-up to

VDD_3V3_SYS

on

PCIe Clock Request for PCIE1_CLK: Connect to CLKREQ pins on

device/connector(s)

I (Endpoint)

4.7kΩ pull-up to

VDD_3V3_SYS

on

PCIe Reset: Connect to PERST pins on device/connector(s)

PCIe Interface 2 (x1 or x2 – Controller #7. Root Port only)

(PCIE2_TX1_N/P)

CSI4_D0_N/P

Capacitor

Differential Transmit Data Pair: Connect to TX_N/P pins of PCIe

connector or RX_N/P pin of PCIe device through AC cap according

to supported configuration.

(PCIE2_RX1_N/P)

CSI4_D2_N/P

(PCIE2_RX0_N/P)

capacitors near Jetson

Xavier NX pins or

device if device on

Differential Receive Data Pair: Connect to RX_N/P pins of PCIe

connector or TX_N/P pin of PCIe device through AC cap according

to supported configuration.

Loading...

Loading...