Clock tool example use case: Configure eMIOS to 60 MHz PLL1 with MPC5777C_264MHz

MPC5777C Clock Calculator Guide, Rev. 1, 12/2018

NXP Semiconductors 29

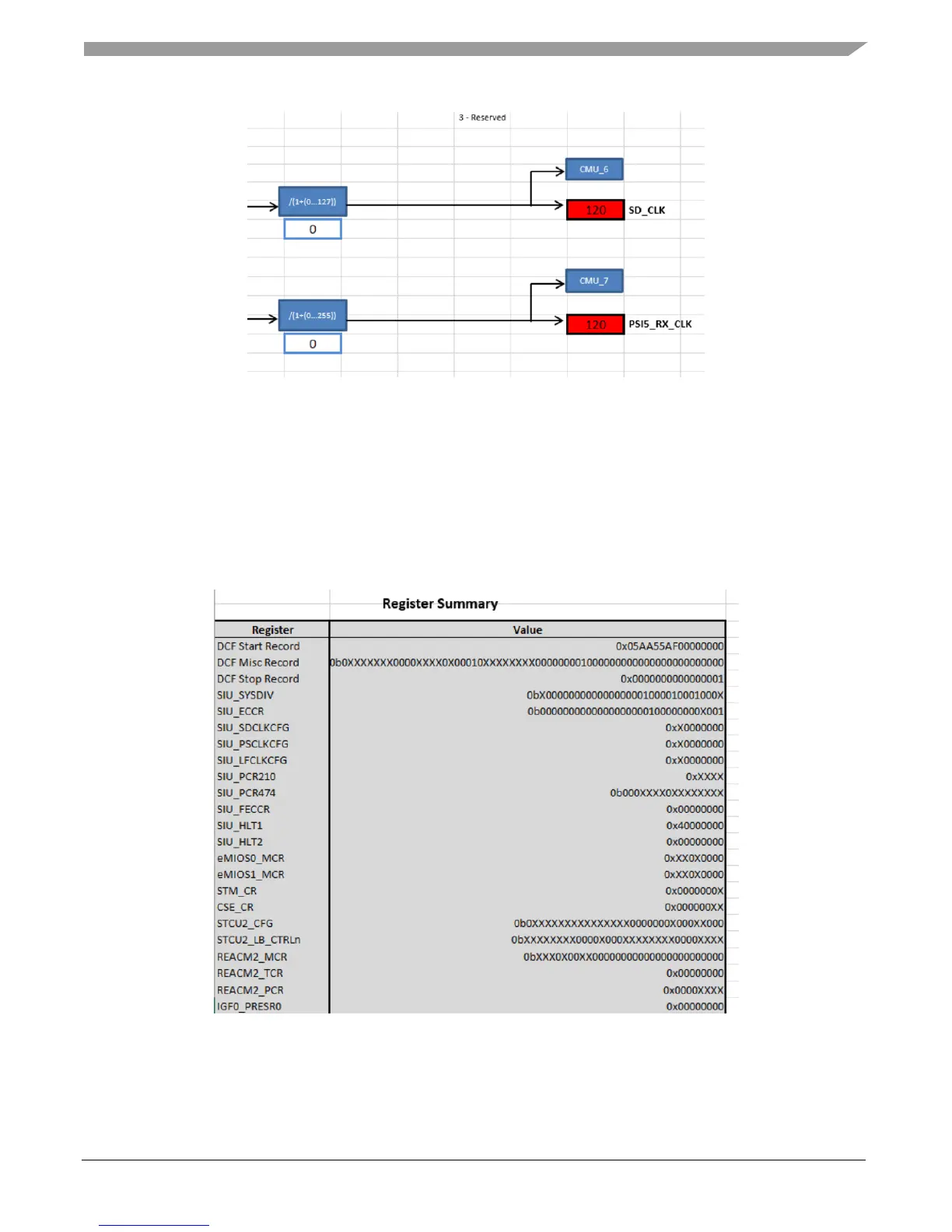

Figure 41. Clock domain exceeds spec

3.3.

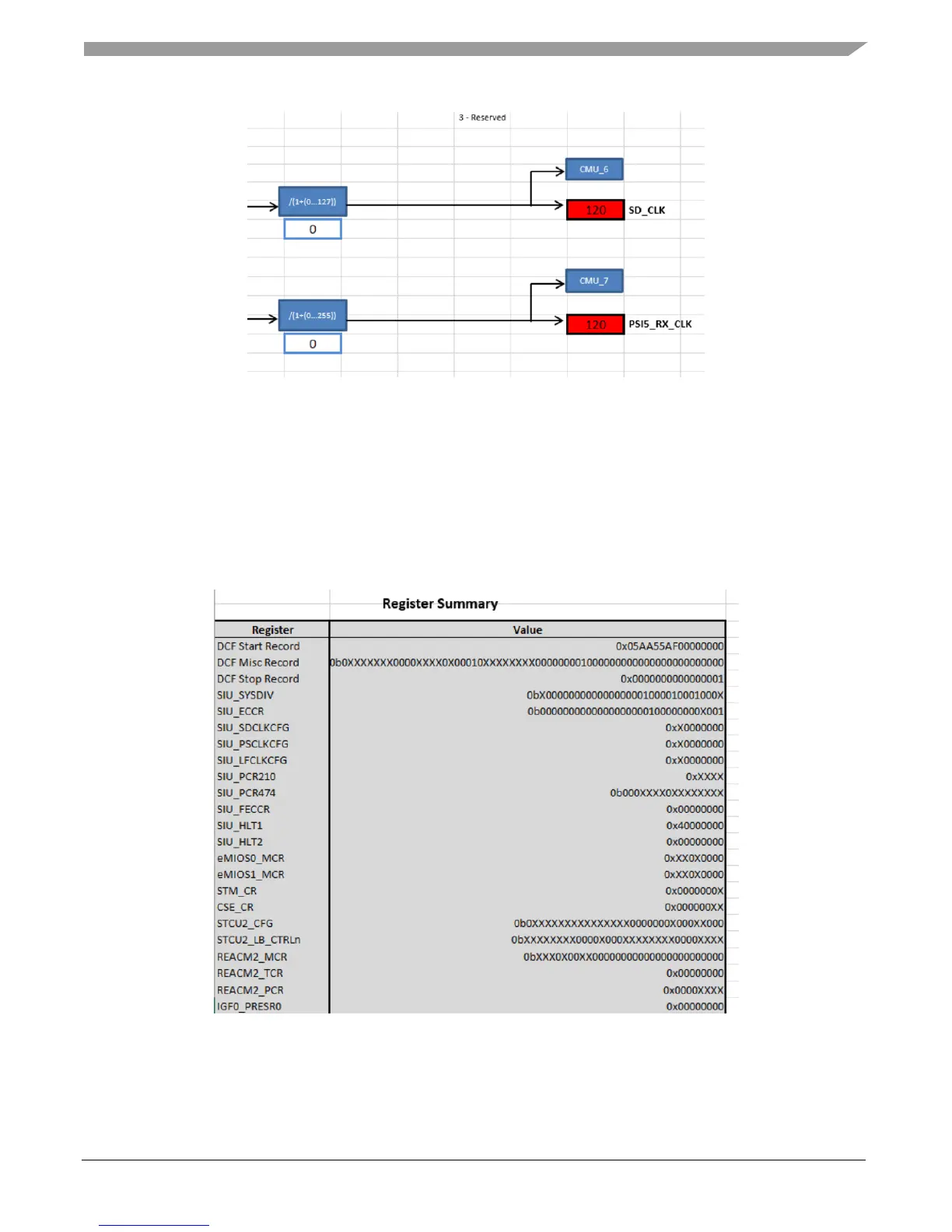

Observe the registers

The final register summary table, as displayed in Summary, is shown in the following figure. Note that

most of these registers would not have to be written in code to achieve the setup that this example just

configured. For example, the register SIU_LFCLKCFG would not have to be included, since the LFAST

was untouched. Registers that would have to be written would be ones like PLLDIG_PLL0DV and

SIU_SYSDIV.

Figure 42. Register summary after configuration

Loading...

Loading...