Circuit Descriptions, Abbreviation List, and IC Data Sheets

EN 214 JL2.1E AA9.

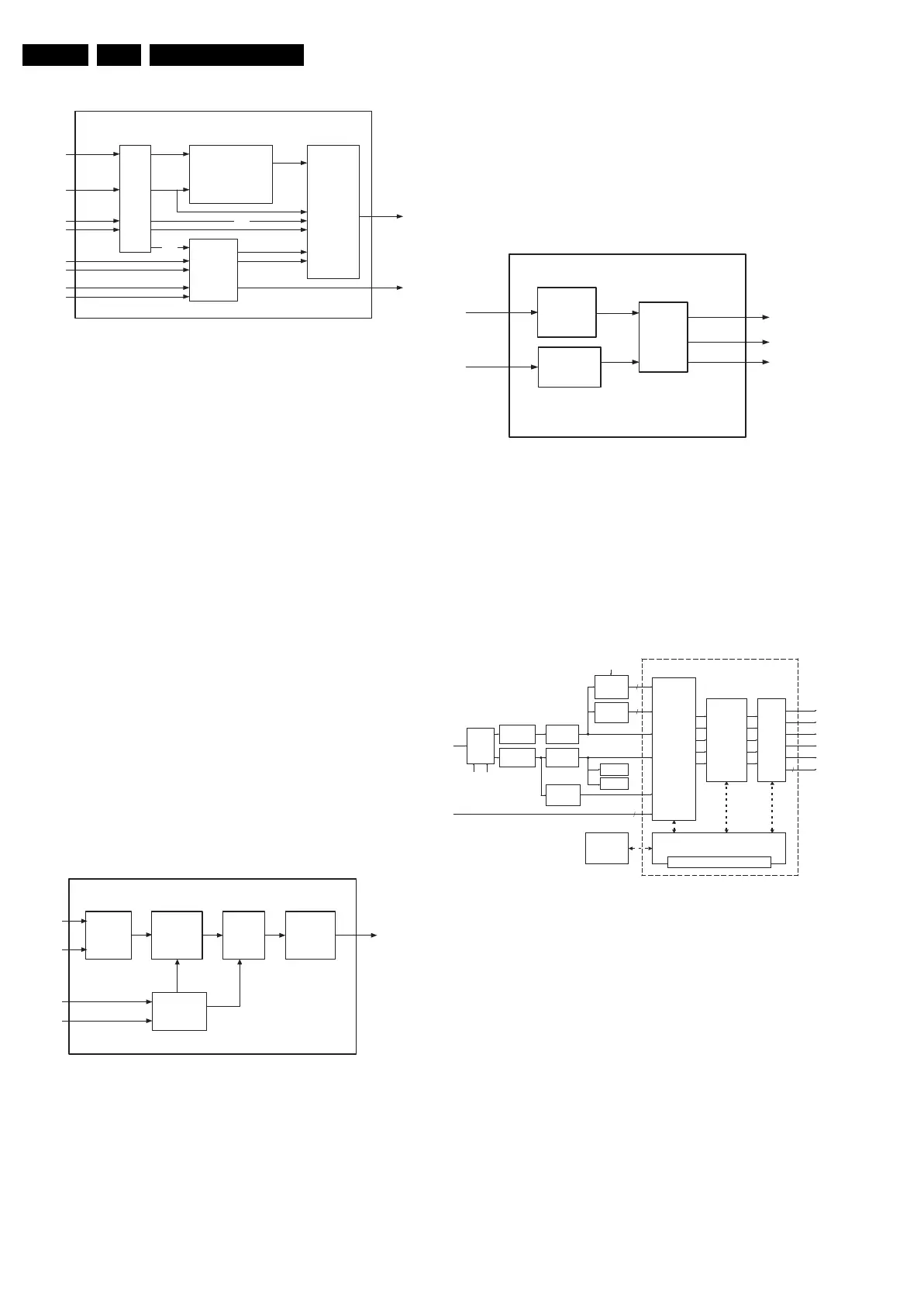

VIDDEC (Video Decoder)

Figure 9-22 VIDDEC block diagram

The CVBS/YC/YUV signals (coming from the I

2

D receiver

block) enter the DMSD block (Digital Multi Standard Decoder)

via the AGC (Automatic Gain Control) block. The multiplexer

block (MUX) takes care of the correct output signal. The sync

signals are processed in the sync block.

The VIDDEC has the following main functions:

• Multi standard colour decoder.

• Automatic system recognition.

• Fully programmable static or automatic (AGC) for all

analog video base band signals.

• AGC on sync amplitude in digital domain.

• Selectable peak white control.

• AGC for chrominance (PAL and NTSC only).

• Programmable Luminance and Chrominance bandwidth

for CVBS and Y/C sources.

• Programmable clamp window for the selected video base

band signals.

• Digital PLL for synchronization on 2fH and ATSC

standards.

• Horizontal (including 3-level sync for 2fH) and vertical sync

detection.

• Automatic detection of 50/60Hz ATSC field frequency.

• Adaptive 2/4-line delay comb filter for two-dimensional

Chrominance/Luminance separation.

• Copy protected source detection according to MacroVision

up to version 7.01

• Possibility of RGB insertion through fast blanking in CVBS

input mode, not in Y/C.

DCU (Data Capturing Unit)

Figure 9-23 DCU block diagram

The purpose of this block is to acquire digital data (containing

Teletext, Closed Captions, ...) from a CVBS/Y/C video input

source. It performs processing on the received data and

provides the data to the ITU-656 formatter unit.

The decimator reduces the sample rate (from 27 MHz to 13.5

MHz) of the incoming digitized CVBS or Y data stream from the

I

2

D receiver. From the video input, the data slicer reconstructs

the transmitted bit stream and associated clock. The SERPAR

block converts the serial bits, coming from the data slicer, into

parallel bytes. The packet processor performs data decoding

and some error correction, assembles received bytes into

packet structure, and streams out the data to the ITU-656

formatter.

The acquisition-timing block locks onto sync signals, and

provides timing information to the other blocks of the data

capture unit.

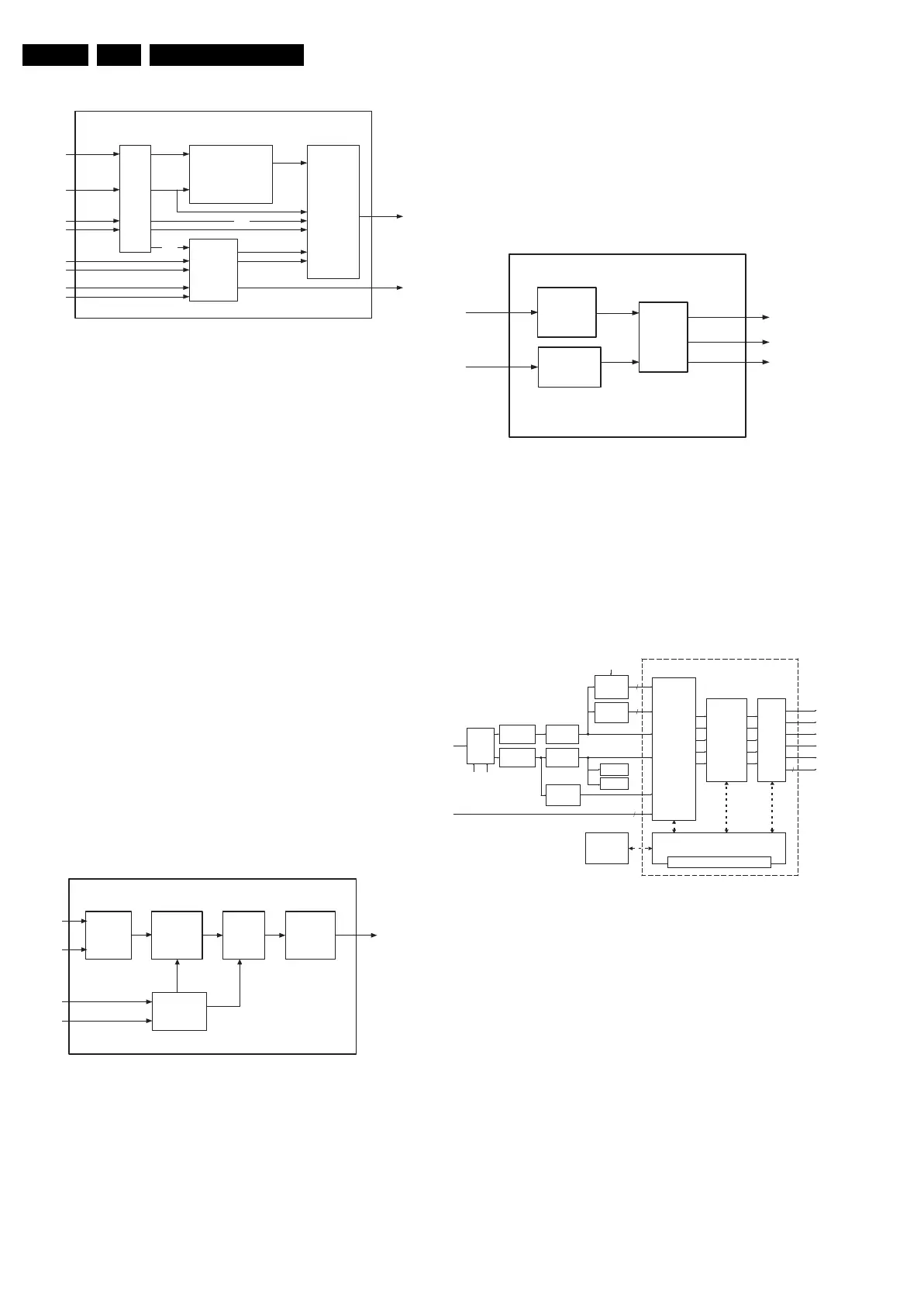

ITU656 Output Formatter

Figure 9-24 ITU656 formatter block diagram

The ITU656 formatter gets YUV data as video input signal,

coming from the VIDDEC block. These YUV data are either

decoded CVBS signals, matrixed RGB signals, or YUV input

signals. The second input data are VBI sliced data coming from

the DCU. The output of the ITU delivers a data stream, which

is ITU-601/656/1364 compliant, and includes video as well as

the VBI data.

DEMDEC (Demodulator and Decoder)

Figure 9-25 DEMDEC block diagram

The demodulator and decoder (DEMDEC) is responsible for

demodulating and decoding incoming SIF signals.

The main features of the DEMDEC are:

• Auto Standard Detection (ASD).

• DQPSK demodulation for different standards,

simultaneously with 1-channel demodulation.

• NICAM decoding (B/G, I, D/K, and L standard).

• Two-carrier multi standard FM demod. (B/G, D/K and M).

• Optional AM demodulation for system L, simultaneously

with NICAM.

• Identification A2 systems (B/G, D/K and M standard) with

different identification time constants.

• FM pilot carrier present detector.

• BTSC MPX decoder.

• SAP decoder.

• dBx noise reduction.

• Japan (EIAJ) decoder.

• FM radio decoder.

E_14700_071.eps

021104

Video Decoder

Digital Multi

Standard Decoder

(DMSD)

AGC

sync

mux

(Fast blank)

Uyuv

Sync

CVBS/Yyc

Yuv/Cyc

Uyuv

Vyuv

Vsync2

Vsync1

FBL1/Hsync1

FBL2/Hsync

Yyc

Cyc

YUV

YUV

HVsync

FBL2

FBL1

Vyuv

Yuv

E_14700_072.eps

310505

Data Capture Unit

Data SlicerDecimator

Acquisition

Timing

SERPAR

Packet

Formatter

VBI data

packets

I2d Data_1

(cvbs)

I2d Data_2

(Y)

H/V Sync

Field Id

E_14700_073.eps

310505

ITU656 Formatter

Video Data

Processing

VBI Data

Processing

SERPAR

ITU_out (9:0)

YUV

VBI data

packets

ITU_Clk

ITU_DATA_VALID

E_14700_074.eps

300505

down

mixer

decimation

FM / AM

demod.

ch. 1

FM / AM

demod.

ch. 2

NICAM

demod. &

decoder

FM ident

MPX

demod.

SAP / EIAJ

demod.

noise

detector

hardware

control &

status reg.

pre-process

decimation

filters,

deemph.,

dbx,

select

SRC

5 channels

tceles & xirtamed

DDEP (DemDec Easy Programming)

decimation

2

2

4

ADC1,2, PIPMONO, Ext. AM

DEMDEC DSP

DEC L/A

DEC R/B

MONO

SAP

PIPMONO

ADC

SIF

control / status registers (XMEM)

2

f

1

f

2

f

pilot

fs = 27 MHz

Loading...

Loading...