Circuit Descriptions, Abbreviation List, and IC Data Sheets

EN 218 JL2.1E AA9.

9.12.5 Temporal Upconversion For SD Signals

Only necessary with film input, not for video.

9.12.6 Vertical And Horizontal Scaling

Necessary when we have progressive frames on the correct

output rate, but still not the correct resolution. This requires

spatial horizontal and vertical upscaling to the correct output

resolution.

9.12.7 PixelPlus 2 Processing

The Pixel plus 2 core consists out of different modules and

each of them help us to create a sharper image.

• Vertical LTI and horizontal LTI, CTI.

• Vertical and horizontal peaking.

• Skin tone depending peaking.

• Colour features.

• Peaking dependent colour saturation.

9.13 VIPER 2 (PNX 8550)

9.13.1 Introduction

The PNX8550 is a highly integrated media processor intended

for deployment in analog, digital, and hybrid TV receivers. It

can be used for 100 Hz interlaced as well as 60 Hz progressive

screens. It is fully capable of performing advanced video

improvement algorithms, such as Digital Natural Motion™, on

Standard Definition analog or digital sources. It includes an HD

capable de-interlacer for converting interlaced HD

transmission signals to progressive output for driving wide-

XGA class Plasma or LCD displays. Two 32-bit 240 MHz VLIW

media processors, referred to as the TriMedia TM3260 CPU

core, carry out the advanced video improvement processing as

well as all audio operations. Fixed hardware functions perform

stable core video functions, such as picture level MPEG2

decoding, scaling, image composition and pixel post

processing.

The PNX8550 provides a primary digital (YUV or RGB) output

to connect to the display specific output processor. In addition,

a secondary analog video output (CVBS or S-Video) for a VCR

is available. This is the so-called DENC-out. It can operate

either in analog PAL/NTSC or digital mode.

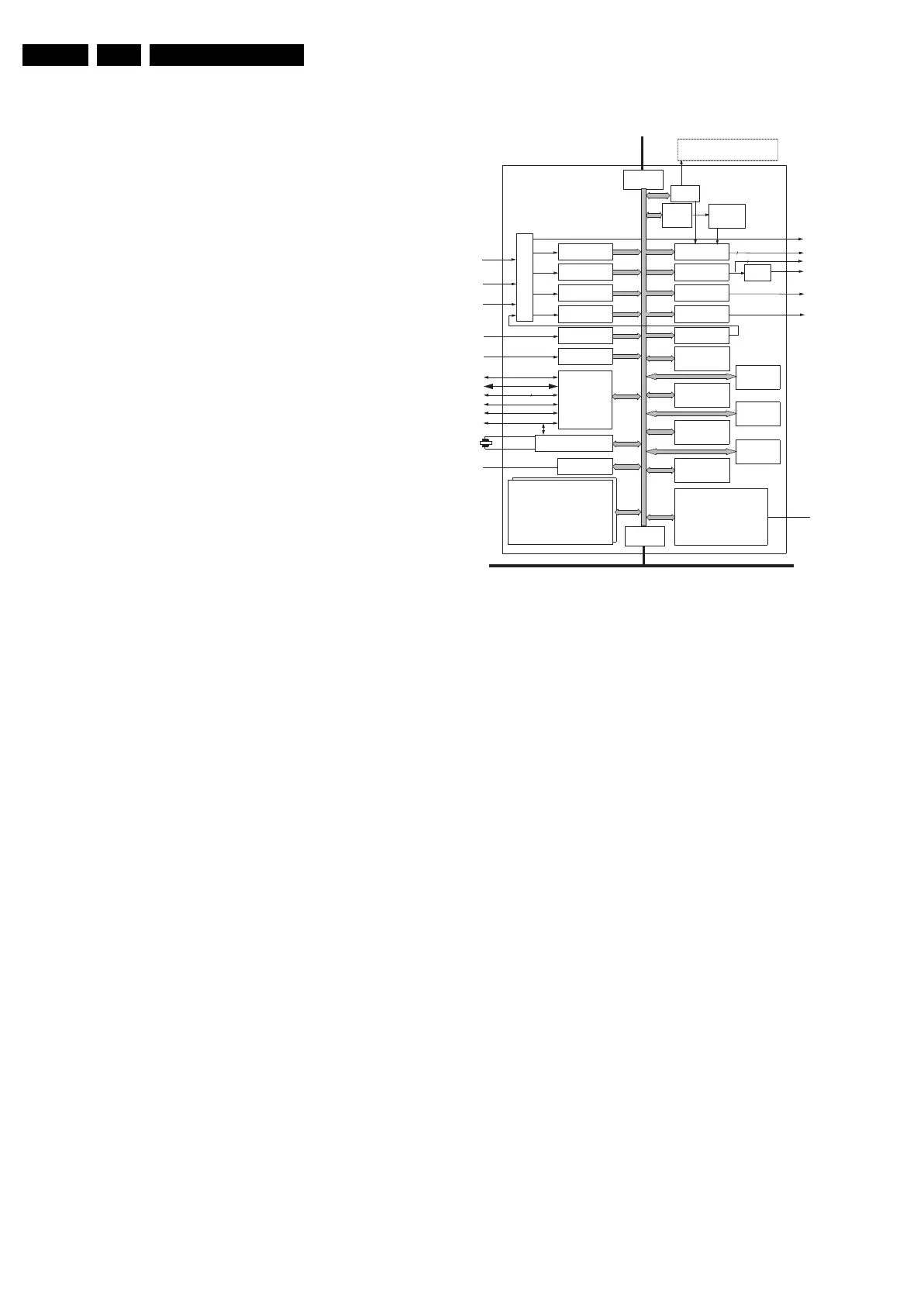

9.13.2 Block Diagram

Figure 9-33 VIPER 2 internal block diagram

Control

An embedded MIPS32 processor (PR4450) running at 266

MHz is available to run the Operating System. The PR4450

processor is primarily responsible for running the demand

paged graphics-intensive operating system, while the TM3260

media processors are responsible for running all real-time

media functions. All hardware resources inside the PNX8550

are accessible by both the MIPS processor and the TM3260

CPUs. A "'sandbox" style system protection provision ensures

that selected MIPS memory regions and critical peripherals

cannot be corrupted or inspected.

VIP (Video Input Processor)

The Video Input Processors (VIP) handles incoming digital

video and processes it for use by other components of the

PNX8550. It provides the following functions:

• Receives 10-bit YUV4:2:2 digital video data from the

selected DVx video port (input signal coming from the AVIP

or Columbus IC output). The data is dithered down to in-

memory 8-bit data format.

• Performs horizontal down scaling or up scaling by 2x (not

available in HD video capture mode).

• Provides an internal Test Pattern Generator with NTSC,

PAL, and variable format support.

• Acquire VBI data using a separate acquisition window from

the video acquisition window.

• ANC header decoding or window mode for VBI data

extraction.

• Interrupt generation for VBI or video written to memory

input mode.

• Colour space conversion (mutual exclusive with horizontal

scaling).

• Raw data mode captures of 8- or 10-bit data.

MBS (Memory Based Scaler)

The PNX8550 contains a Memory Based Scaler that performs

operation on images in main memory. The MBS can either be

controlled task by task by a TM3260, or it can be given a list of

E_14700_076.eps

091104

PCI

33 MHz, 32-bit PCI 2.2

MMI

2xTM3260 Media Processor

5 issue, 240 MHz

64 kB

128 32-bit regs

VIP1

VIP2

MSP1

MSP2

retuor 656 & st

DV1 656/TS

656

656

TS

TS

QVCP1

QVCP2

AI1-2

I

2

S audio

SPDI 1-2

SPDIF audio

AO1-2

SPDO

misc. I/O,

UART1-2

Gen. Purpose I/O

16

MBS

2x225 MHz, 32-bit wide DDR

JTAG

27 MHz

xtal

DV2* 656/TS

DV3 656/TS

(includes NAND/nor flash, IDE drive and 68k peripheral capability)

USB host i/f (2 port)

bound. scan

Smartcard1-2

PR4450 MIPS CPU

250 MHz

16 kB

MMU

EJTAG debug

TSDMA

boot, reset, clock

VMPG

DE (2D)

E-DMA

I

2

C (4x)

16 kB 2-port

16 kB

(1 HD or 2 SD)

QTNR

VLD2

DVD-CSS

Remote Control

I

2

S audio

SPDIF audio

QVCP5L_OUT

QVCP2L_OUT

TS_OUT

656/HD/VGA

DENC

656

analog Y/C,cvbs

30

10

8 ch + 8 ch

PNX8550

timers/

counters,

semaphores

TM-DBG (2x)

Tunnel

Optional external coprocessors

Peak rate: 12bit/cycle each way

including video enhancement chip

V Peaking

MBS2

Loading...

Loading...