Vectored Interrupt Controller (VIC) 105 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

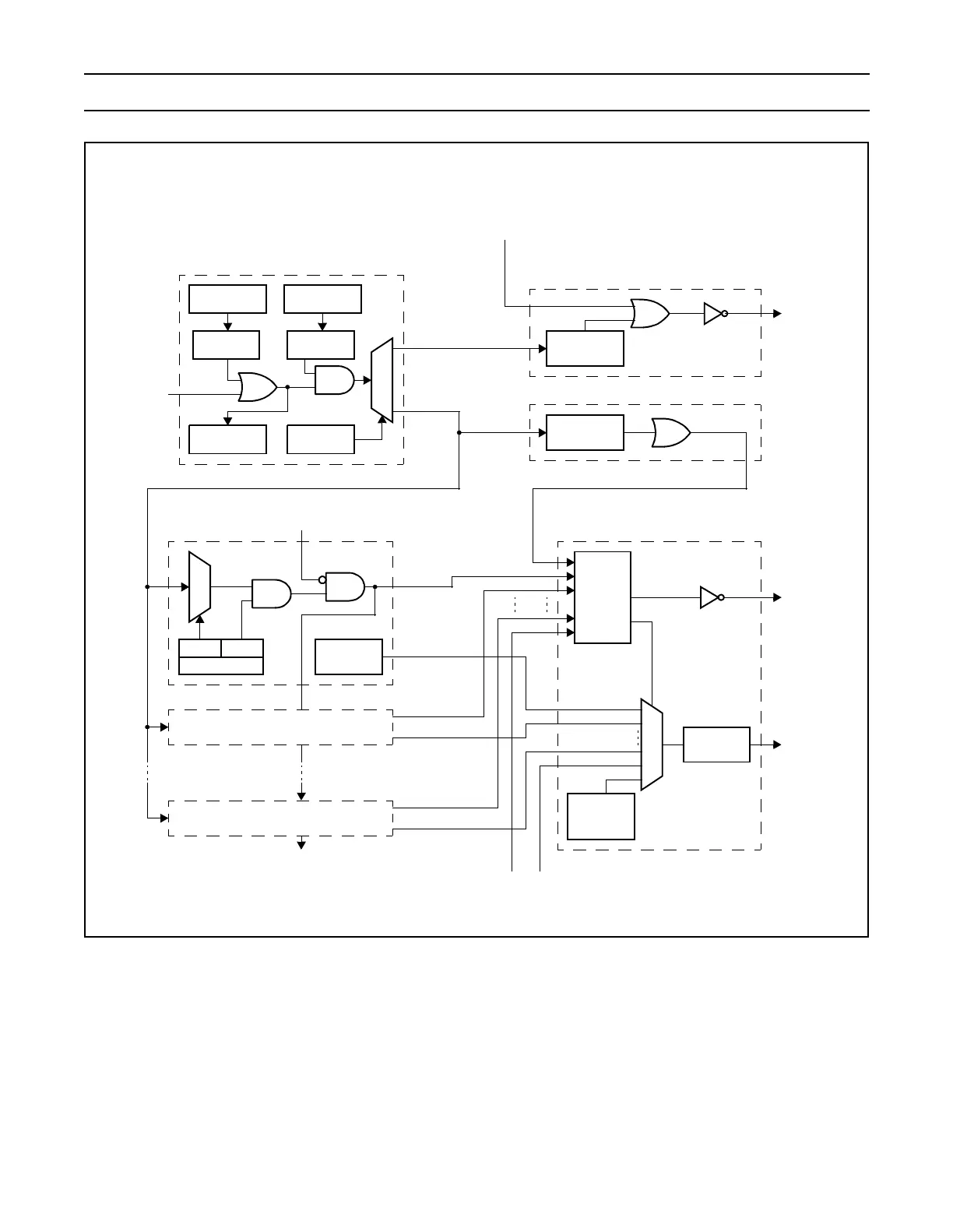

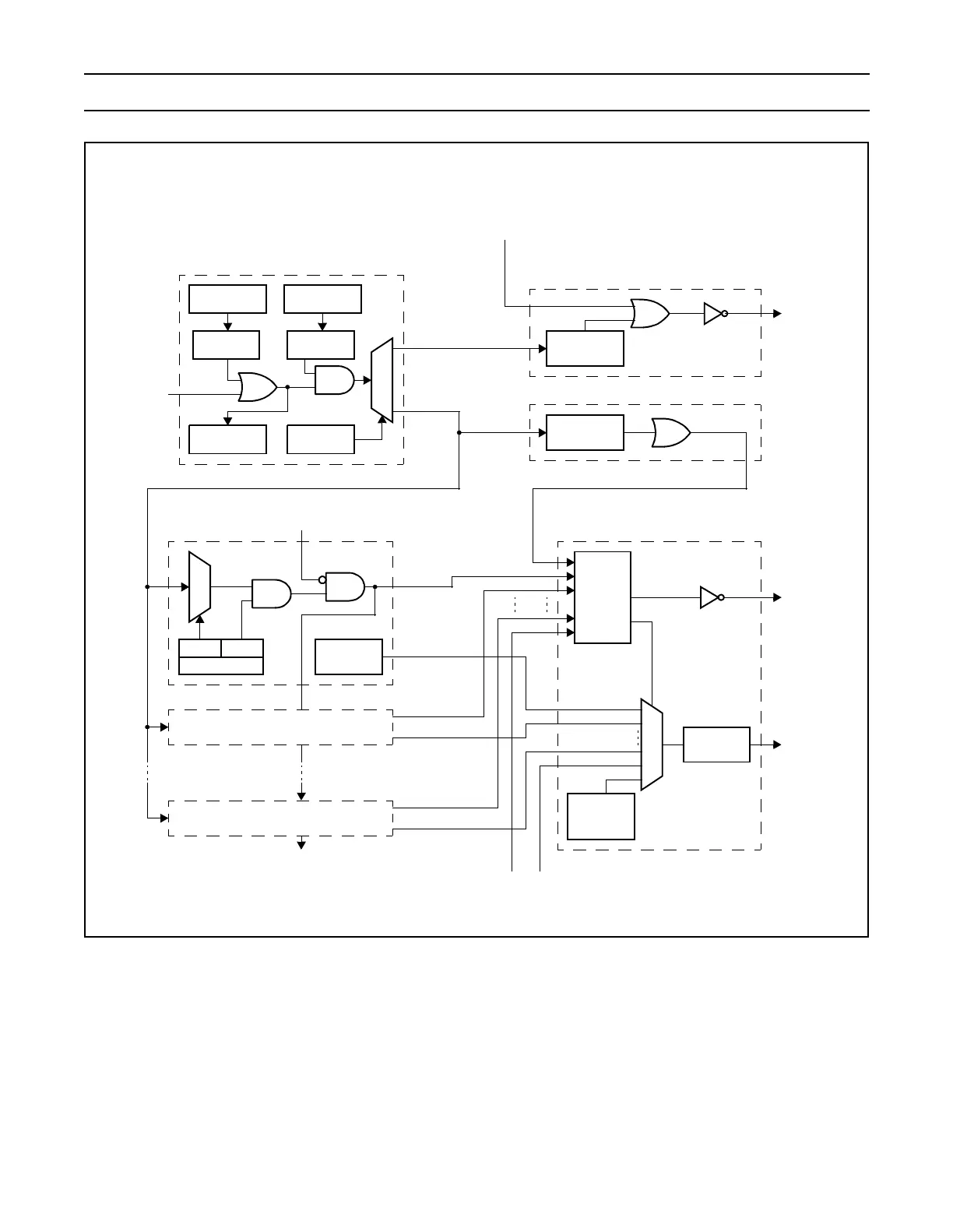

Figure 19: Block Diagram of the Vectored Interrupt Controller

RawInterrupt

[31:0]

IntSelect

[31:0]

IntEnable

[31:0]

SoftInt

[31:0]

VICINT

SOURCE

[31:0]

FIQStatus

[31:0]

IRQStatus

[31:0]

Interrupt Request, Masking, and Selection

VectorAddr

[31:0]

VectIRQ0

VectAddr0[31:0]

Vector Interrupt 0

Priority 0

VectorCntl[5:0]

Source Enable

VectIRQ1

VectAddr1[31:0]

Vector Interrupt 1 Priority 1

Priority 2

VectIRQ15

VectAddr15[31:0]

Vector Interrupt 15 Priority 14

Priority 15

Hardware

Priority

Logic

Default

VectorAddr

[31:0]

VectorAddr

[31:0]

VICVECTADDRIN[31:0]nVICIRQIN

IRQ

nVICIRQ

VICVECT

ADDROUT

[31:0]

Interrupt Priority Logic

Address Select for

Highest Priority

Interrupt

nVICFIQ

FIQStatus

[31:0]

nVICFIQIN

Non-vectored FIQ Interrupt Logic

NonVectIRQ

IRQStatus

[31:0]

Non-vectored IRQ Interrupt Logic

IRQ

SoftIntClear

[31:0]

IntEnableClear

[31:0]

Loading...

Loading...