CAN Controllers and Acceptance Filter 192 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2292/2294ARM-based Microcontroller

Mode Register (CANMOD - 0xE00x x000)

This register controls the basic operating mode of the CAN Controller. Bits not listed read as 0 and should be written as 0. See

Table 124 for details on specific CAN channel register address.

Note 1: The LOM and STM bits can only be written if the RM bit is 1 prior to the write operation.

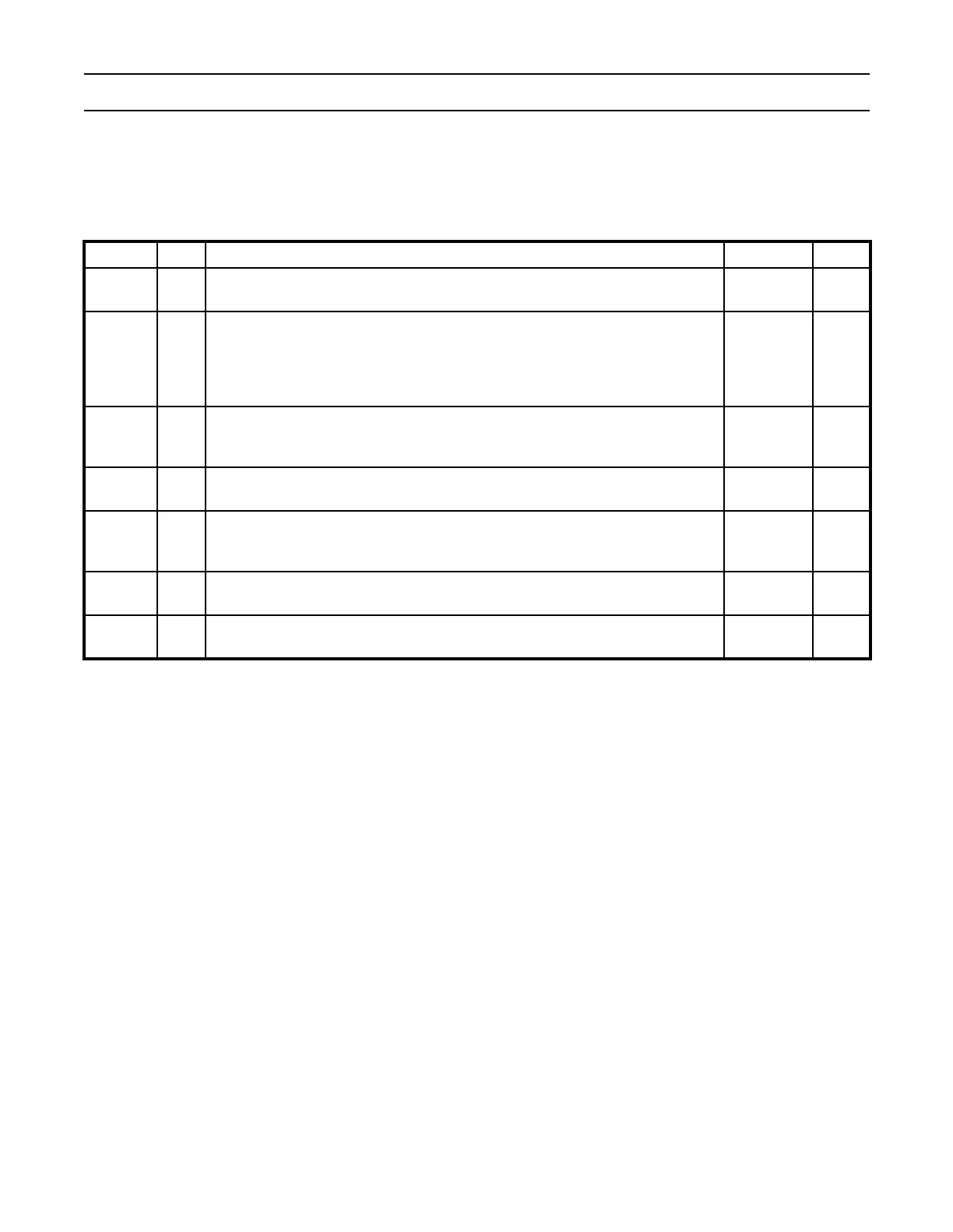

Table 125: CAN Mode Register (CANMOD - 0xE00x x000)

CANMOD Name Function Reset Value RM Set

0RM

0: the CAN Controller operates, and certain registers can not be written.

1: Reset Mode -- CAN operation is disabled, and writable registers can be written.

11

1LOM

0: the CAN controller acknowledges a successfully-received message on its CAN.

1: Listen Only Mode -- the controller gives no acknowledgment on CAN, even if a

message is successfully received. Messages cannot be sent, and the controller

operates in “error passive” mode. This mode is intended for software bit rate

detection and “hot plugging”.

0X

2STM

0: a transmitted message must be acknowledged to be considered successful.

1: Self Test Mode -- the controller will consider a Tx message successful if there is

no acknowledgment. Use this state in conjunction with the SRR bit in CANCMR.

0X

3TPM

0: the priority of the 3 Transmit Buffers depends on their CAN IDs.

1: the priority of the 3 Transmit Buffers depends on their Tx Priority fields.

0X

4SM

0: normal operation

1: Sleep Mode -- the CAN controller sleeps if it is not requesting an interrupt, and

there is no bus activity. See the Sleep Mode description on page 203.

00

5RPM

0: RX and TX pins are Low for a dominant bit.

1: Reverse Polarity Mode -- RX pins are High for a dominant bit.

00

7TM

0: normal operation

1: Test Mode. The state of the RX pin is clocked onto the TX pin.

00

Loading...

Loading...