System Control Block 82 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

Power Control for Peripherals Register (PCONP - 0xE01FC0C4)

The PCONP register allows turning off selected peripheral functions for the purpose of saving power. A few peripheral functions

cannot be turned off (i.e. the Watchdog timer, GPIO, the Pin Connect block, and the System Control block). Each bit in PCONP

controls one of the peripherals. The bit numbers correspond to the related peripheral number as shown in the VPB peripheral

map in the LPC2119/2129/2292/2294 Memory Addressing section.

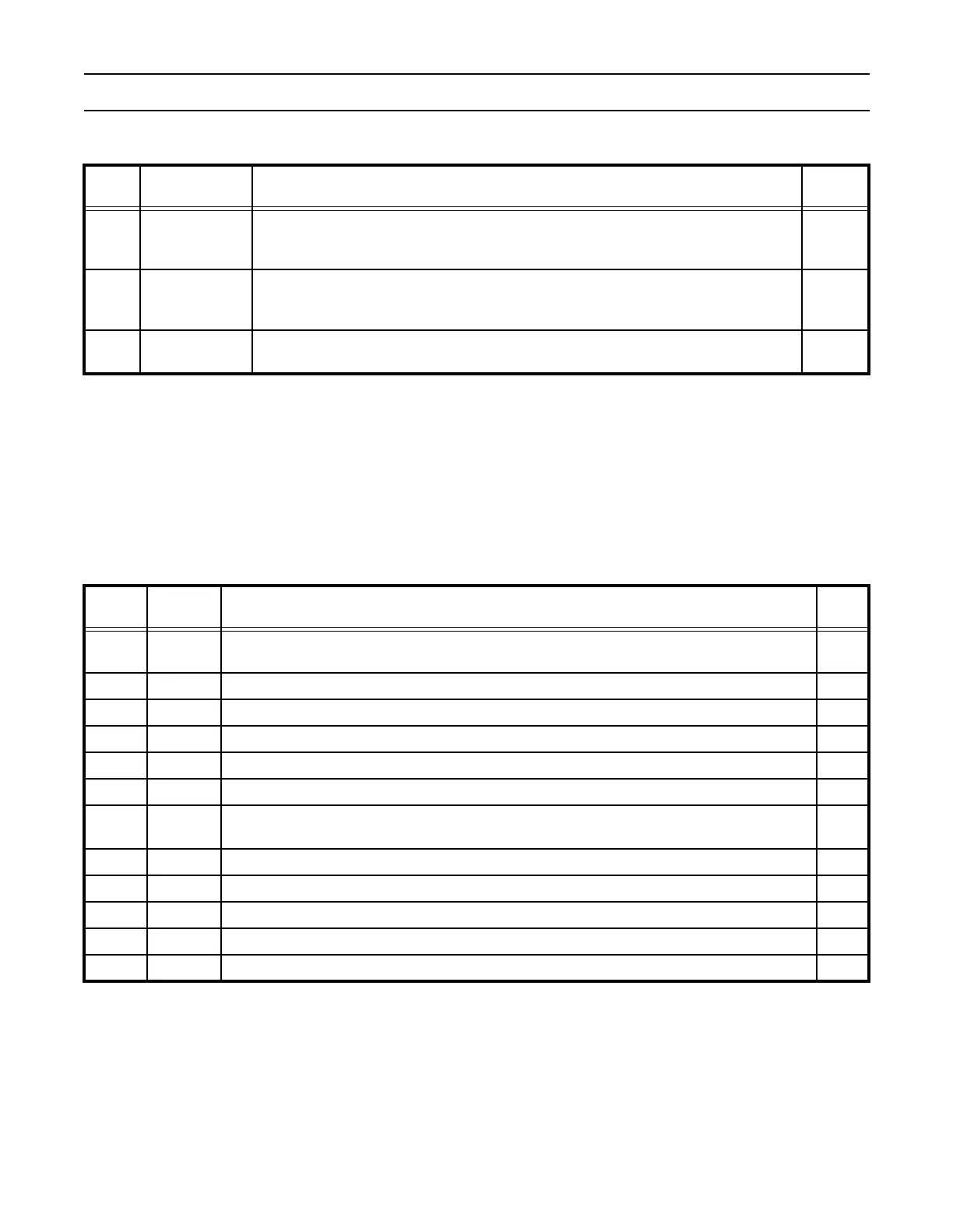

Table 30: Power Control Register (PCON - 0xE01FC0C0)

PCON Function Description

Reset

Value

0IDL

Idle mode - when 1, this bit causes the processor clock to be stopped, while on-chip

peripherals remain active. Any enabled interrupt from a peripheral or an external interrupt

source will cause the processor to resume execution.

0

1PD

Power Down mode - when 1, this bit causes the oscillator and all on-chip clocks to be

stopped. A wakeup condition from an external interrupt can cause the oscillator to re-

start, the PD bit to be cleared, and the processor to resume execution.

0

7:2 Reserved

Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

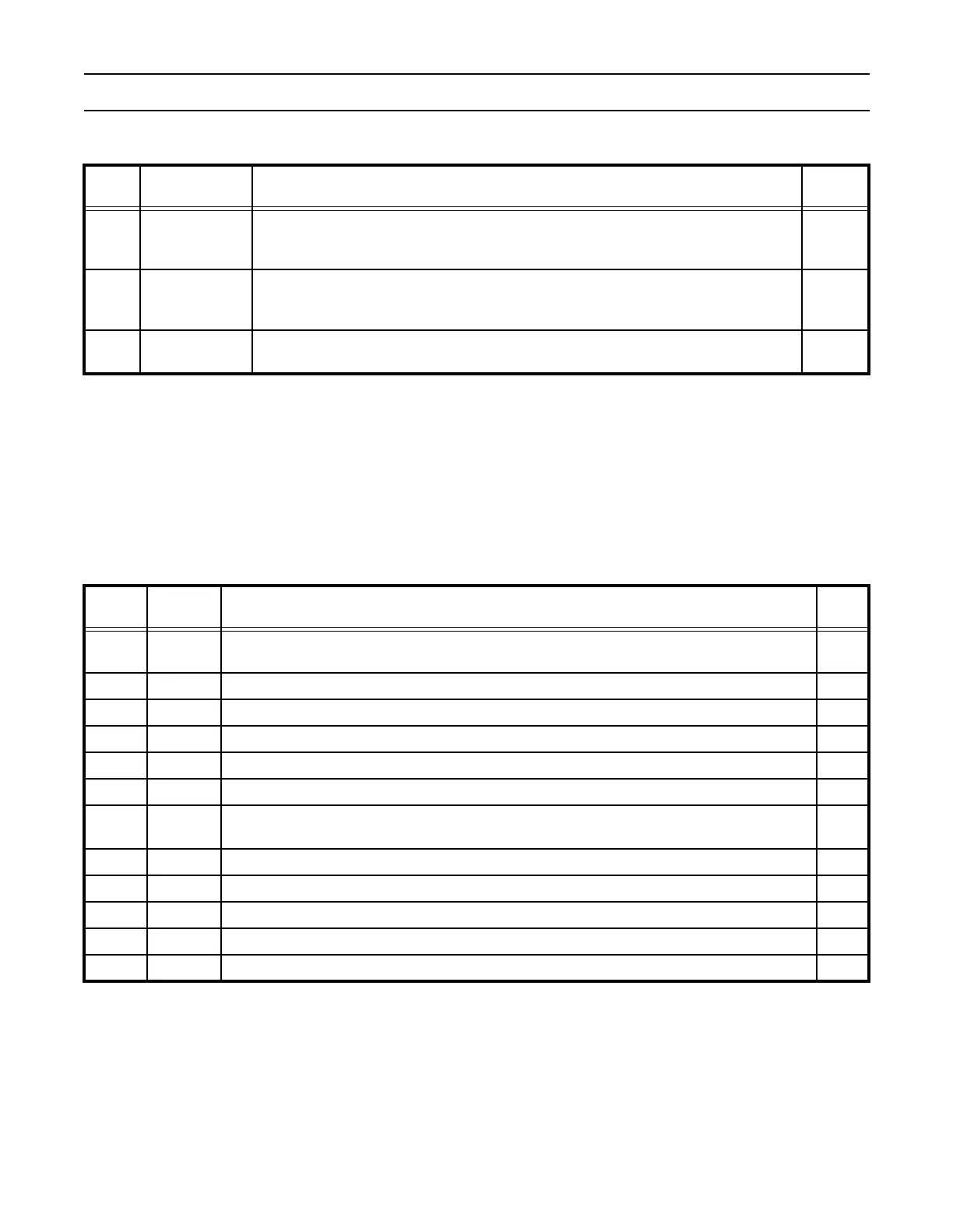

Table 31: Power Control for Peripherals Register for LPC2119/2129/2292 (PCONP - 0xE01FC0C4)

PCONP Function Description

Reset

Value

0 Reserved

Reserved, user software should not write ones to reserved bits. The value read from a reserved

bit is not defined.

0

1 PCTIM0 When 1, TIMER0 is enabled. When 0, TIMER0 is disabled to conserve power. 1

2 PCTIM1 When 1, TIMER1 is enabled. When 0, TIMER1 is disabled to conserve power. 1

3 PCURT0 When 1, UART0 is enabled. When 0, UART0 is disabled to conserve power. 1

4 PCURT1 When 1, UART1 is enabled. When 0, UART1 is disabled to conserve power. 1

5 PCPWM0 When 1, PWM0 is enabled. When 0, PWM0 is disabled to conserve power. 1

6 Reserved

User software should not write ones to reserved bits. The value read from a reserved bit is not

defined.

0

7 PCI2C When 1, the I

2

C interface is enabled. When 0, the I

2

C interface is disabled to conserve power. 1

8 PCSPI0 When 1, the SPI0 interface is enabled. When 0, the SPI0 is disabled to conserve power. 1

9 PCRTC When 1, the RTC is enabled. When 0, the RTC is disabled to conserve power. 1

10 PCSPI1 When 1, the SPI1 interface is enabled. When 0, the SPI1 is disabled to conserve power. 1

11 Reserved User software should write 0 here to reduce power consumption. 1

Loading...

Loading...