PDP-5071PU

210

1234

1234

C

D

F

A

B

E

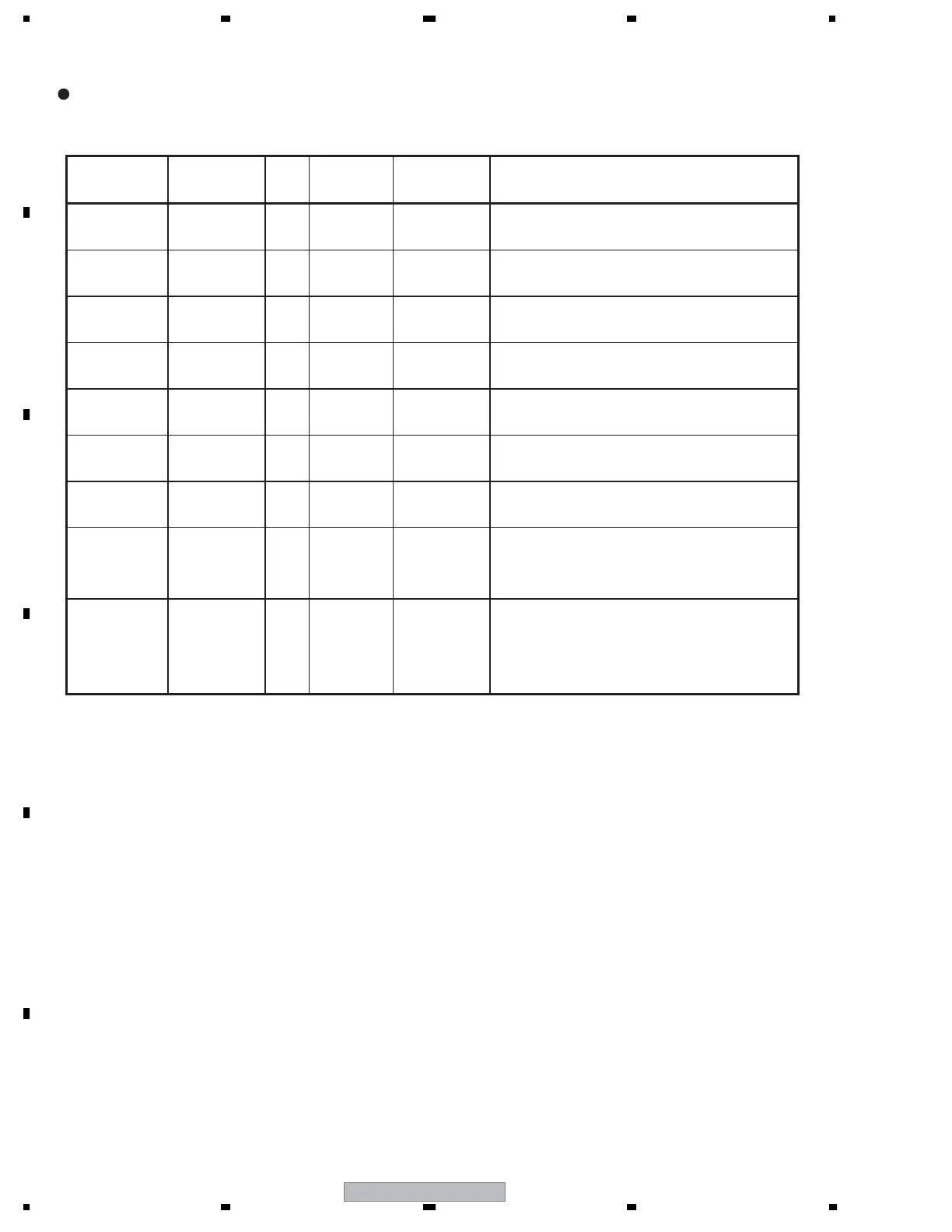

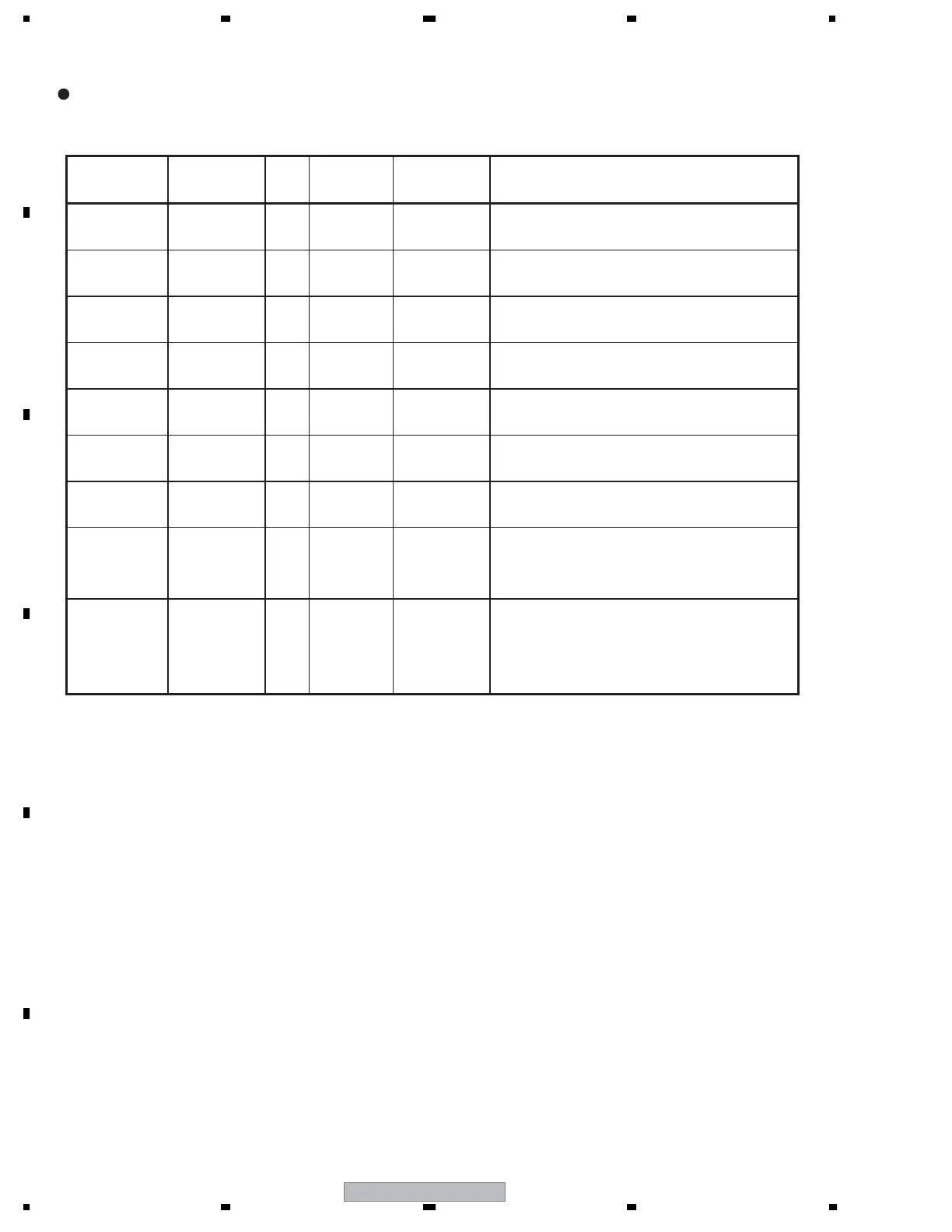

Pin Function

2.15 Memory interface terminal

Acronyms Terminal number I/O Level Buffer type

PU/PD [kΩ]

Functions

SDRABP 4 O LVTTL

3-state

3 mA All bank pre-charge output for external memory

(Active-High)

SDRCLK 25 O LVTTL

3-state

9 mA Clock output for external memory

SDRCKE 21 O LVTTL

3-state

3 mA Clock enable output for external memory

(Active-High)

SDRCS 20 O LVTTL

3-state

3 mA Chip select output for external memory

(Active-Low)

SDRCAS 28 O LVTTL

3-state

3 mA Column address strobe output for external memory

(Active-Low)

SDRRAS 22 O LVTTL

3-state

3 mA Low address strobe output for external memory

(Active-Low)

SDRWE 29 O LVTTL

3-state

3 mA Write enable output for external memory

(Active-Low)

SDRA0

-SDRA11

19,18,15,14,

13,12,10,9,8,

7,6,5

O LVTTL

3-state

3 mA Address output for external memory

Insert a damping resistor of approximately 100Ω,

and connect to the SDRAM address terminal.

SDRDQ0

-SDRDQ15

51,49,46,42,

40,36,34,30,

31,35,37,41,

43,47,50,52

I/O LVTTL

3-state

6 mA Data input/output for external memory.

Loading...

Loading...