Hardware description

10.4 Input/output address areas

SIMATIC IPC127E

Operating Instructions, 01/2019, A5E44296915-AA

79

10.4.2 Watchdog register

Excerpt from Intel® technical specifications

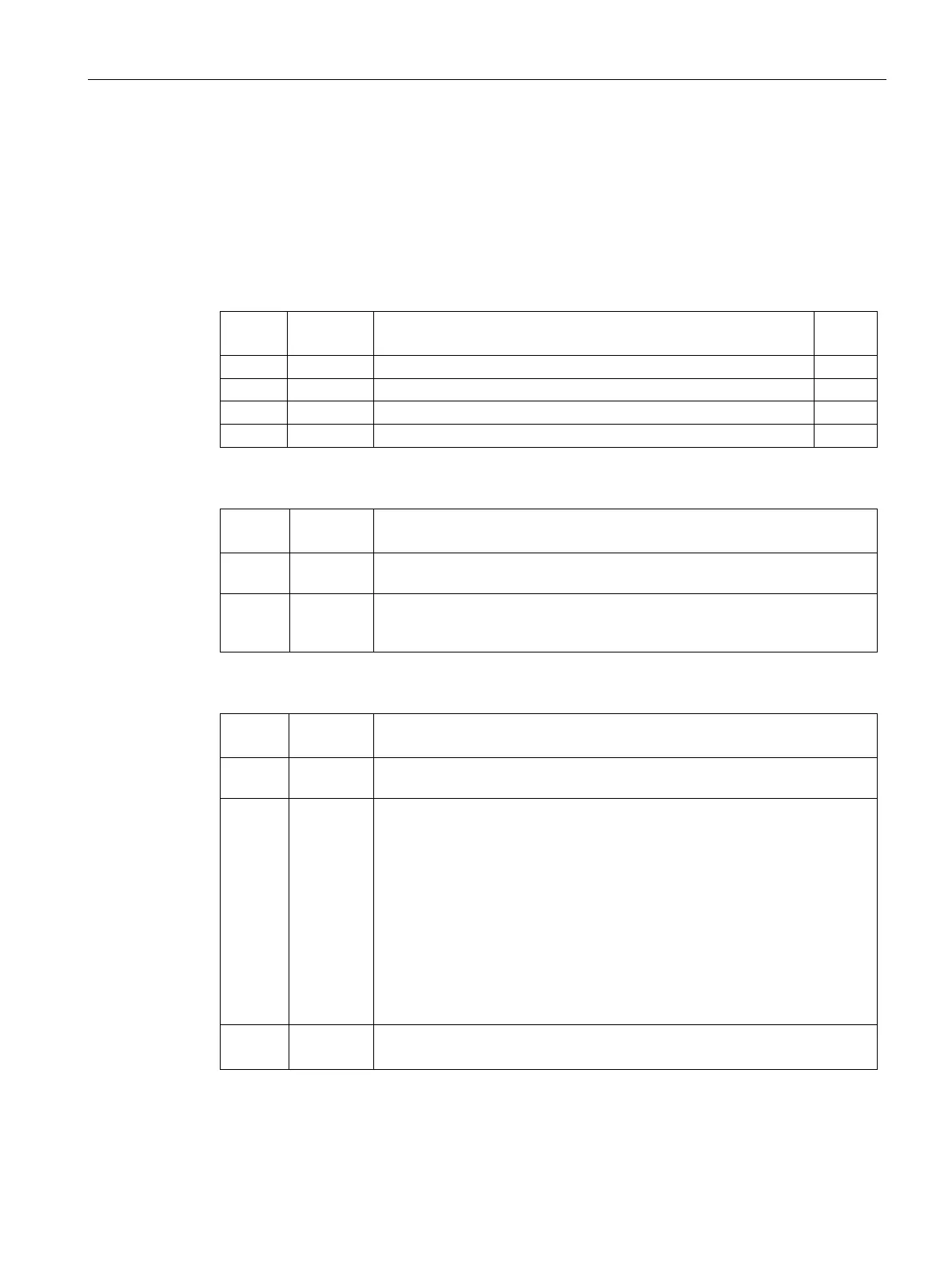

TCO IO Register

ACPI IO Base Address= 0x400

TCO Register = ACPI IO Adr + TCO Offset

Register Name (ID) - Offset

TCO Reload Register (TCO_RLD) - Offset 60h

TCO Timer Status (TCO_STS) - Offset 64h

TCO Timer Control (TCO1_CNT) - Offset 68h

TCO Timer Register (TCO_TMR) - Offset 70h

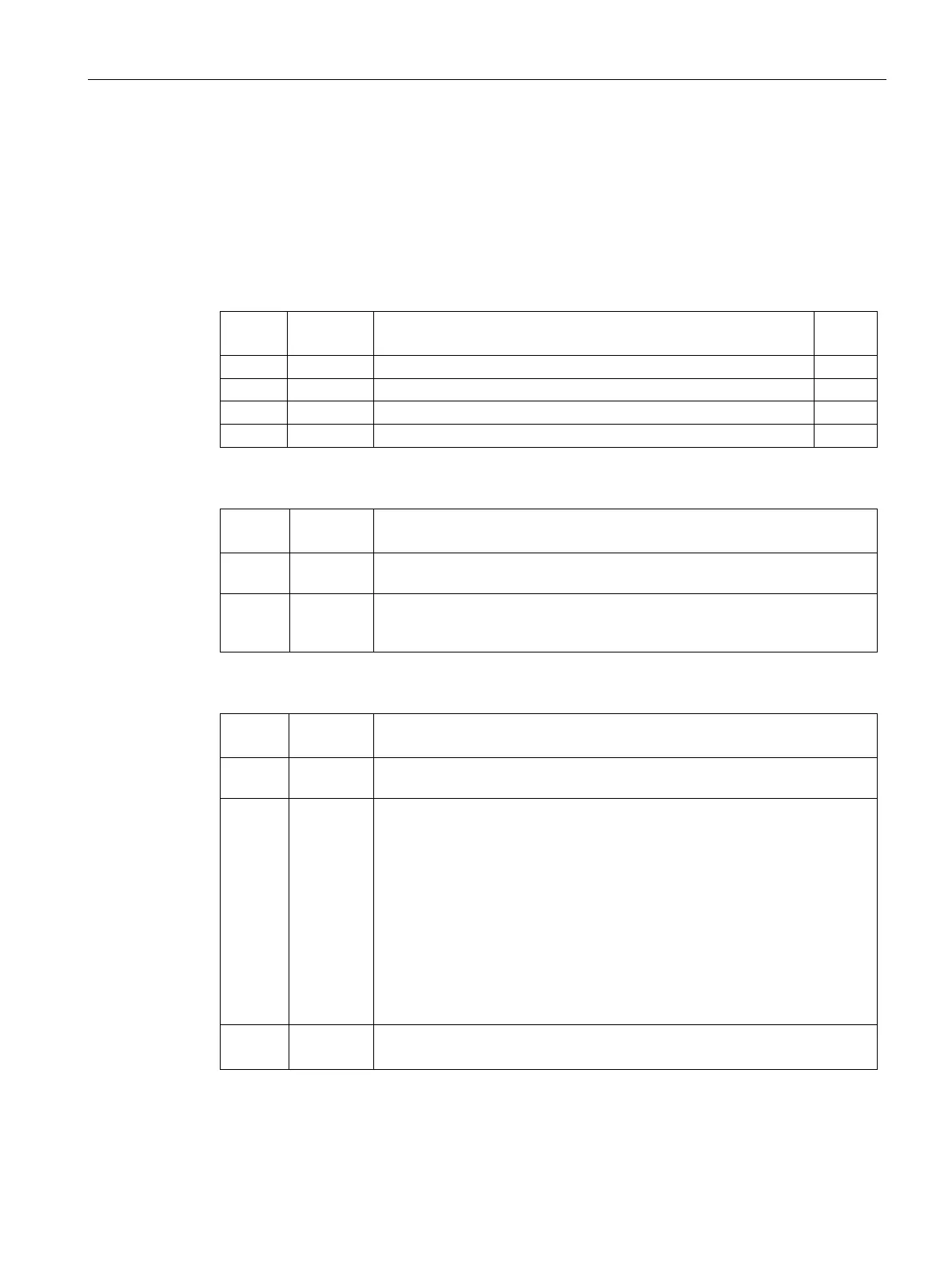

TCO Reload Register (TCO_RLD) - Offset 60h

Field Name (ID): Description

31:10 0h

Reserved.

9:0 0h

RO/V

TCO Timer Value (tco-val):

Reading this register will return the current count

of the TCO timer. Writing any value to this register will reload the timer to

TCO Timer Status (TCO_STS) - Offset 64h

Field Name (ID): Description

31:18 0h

Reserved.

17 0h

RW/1C/V

Second Timeout Status (second_to_sts):

PMC sets this bit to 1 to indicate

that the TIMEOUT bit had been (or is currently) set and a second timeout

occurred before the TCO_RLD register was written. If this bit is set and the

NO_REBOOT config bit is 0, then the PMC will reboot the system after sec-

ond timeout. The reboot is done by interrupting the Arc and starting a reset

flow based on the OS_POLICY. This bit is only cleared by writing a 1 to this

bit or by a reset.

On some prior platforms, this field is reset on RSMRST_B, a reset signal

based on a RSMRST# pin that indicates the suspend/resume voltages are

stable.

This field is reset on RSM_RST_N de-assertion. This field is not reset on cold

reset, warm reset, an Sx.

16:4 0h

RO

: Reserved.

Loading...

Loading...