RM0440 Rev 4 1385/2126

RM0440 General-purpose timers (TIM15/TIM16/TIM17)

1445

30.4.22 External trigger synchronization (TIM15 only)

The TIM timers are linked together internally for timer synchronization or chaining.

The TIM15 timer can be synchronized with an external trigger in several modes: Reset

mode, Gated mode, Trigger mode, Reset + trigger and gated + reset modes.

Slave mode: Reset mode

The counter and its prescaler can be reinitialized in response to an event on a trigger input.

Moreover, if the URS bit from the TIMx_CR1 register is low, an update event UEV is

generated. Then all the preloaded registers (TIMx_ARR, TIMx_CCRx) are updated.

In the following example, the upcounter is cleared in response to a rising edge on tim_ti1

input:

1. Configure the channel 1 to detect rising edges on tim_ti1. Configure the input filter

duration (in this example, we do not need any filter, so we keep IC1F=0000). The

capture prescaler is not used for triggering, so it does not need to be configured. The

CC1S bits select the input capture source only, CC1S = 01 in the TIMx_CCMR1

register. Write CC1P=’0’ and CC1NP=’0’ in the TIMx_CCER register to validate the

polarity (and detect rising edges only).

2. Configure the timer in reset mode by writing SMS=100 in TIMx_SMCR register. Select

tim_ti1 as the input source by writing TS=00101 in TIMx_SMCR register.

3. Start the counter by writing CEN=1 in the TIMx_CR1 register.

The counter starts counting on the internal clock, then behaves normally until tim_ti1 rising

edge. When tim_ti1 rises, the counter is cleared and restarts from 0. In the meantime, the

trigger flag is set (TIF bit in the TIMx_SR register) and an interrupt request, or a DMA

request can be sent if enabled (depending on the TIE and TDE bits in TIMx_DIER register).

The following figure shows this behavior when the auto-reload register TIMx_ARR=0x36.

The delay between the rising edge on tim_ti1 and the actual reset of the counter is due to

the resynchronization circuit on tim_ti1 input.

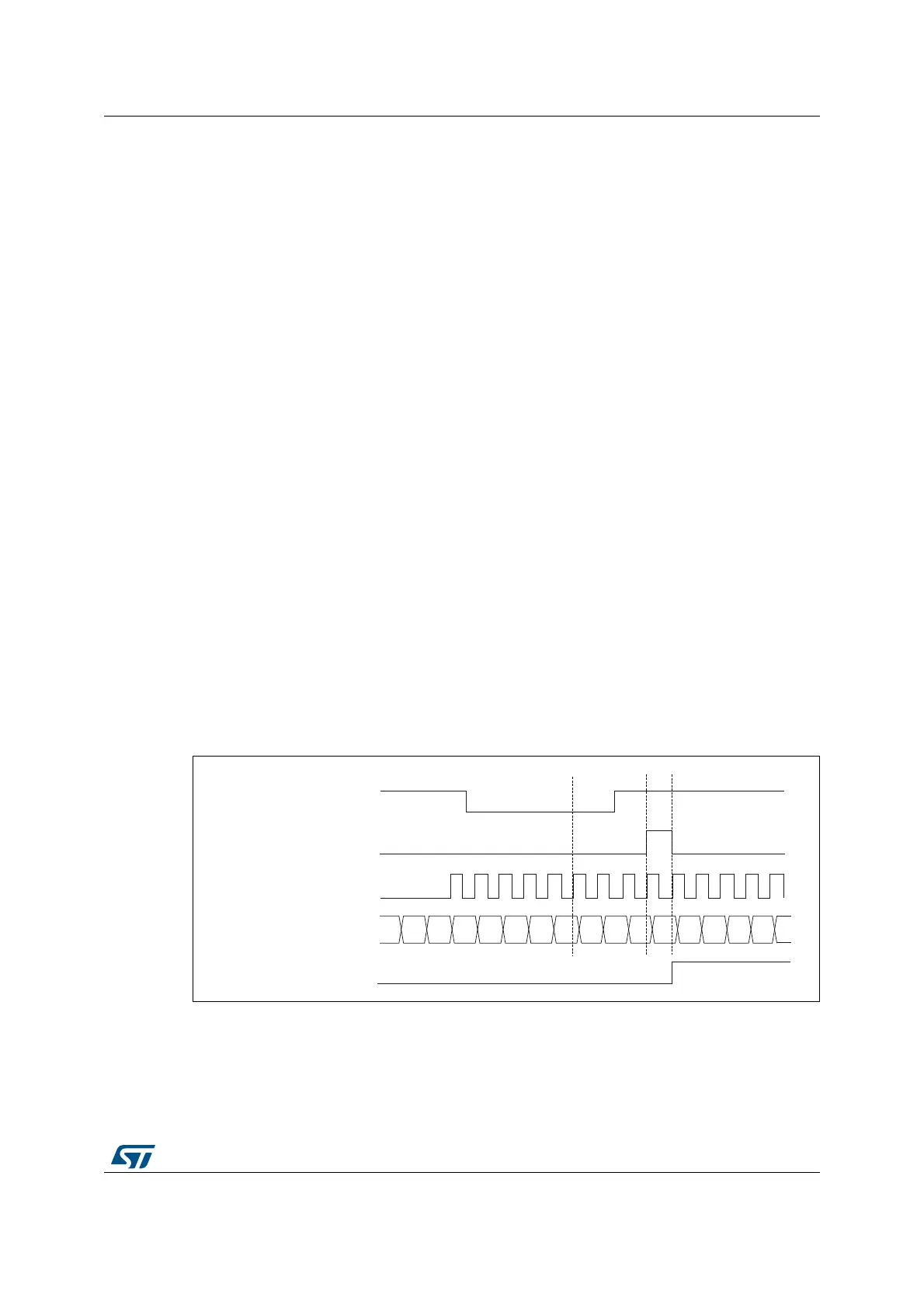

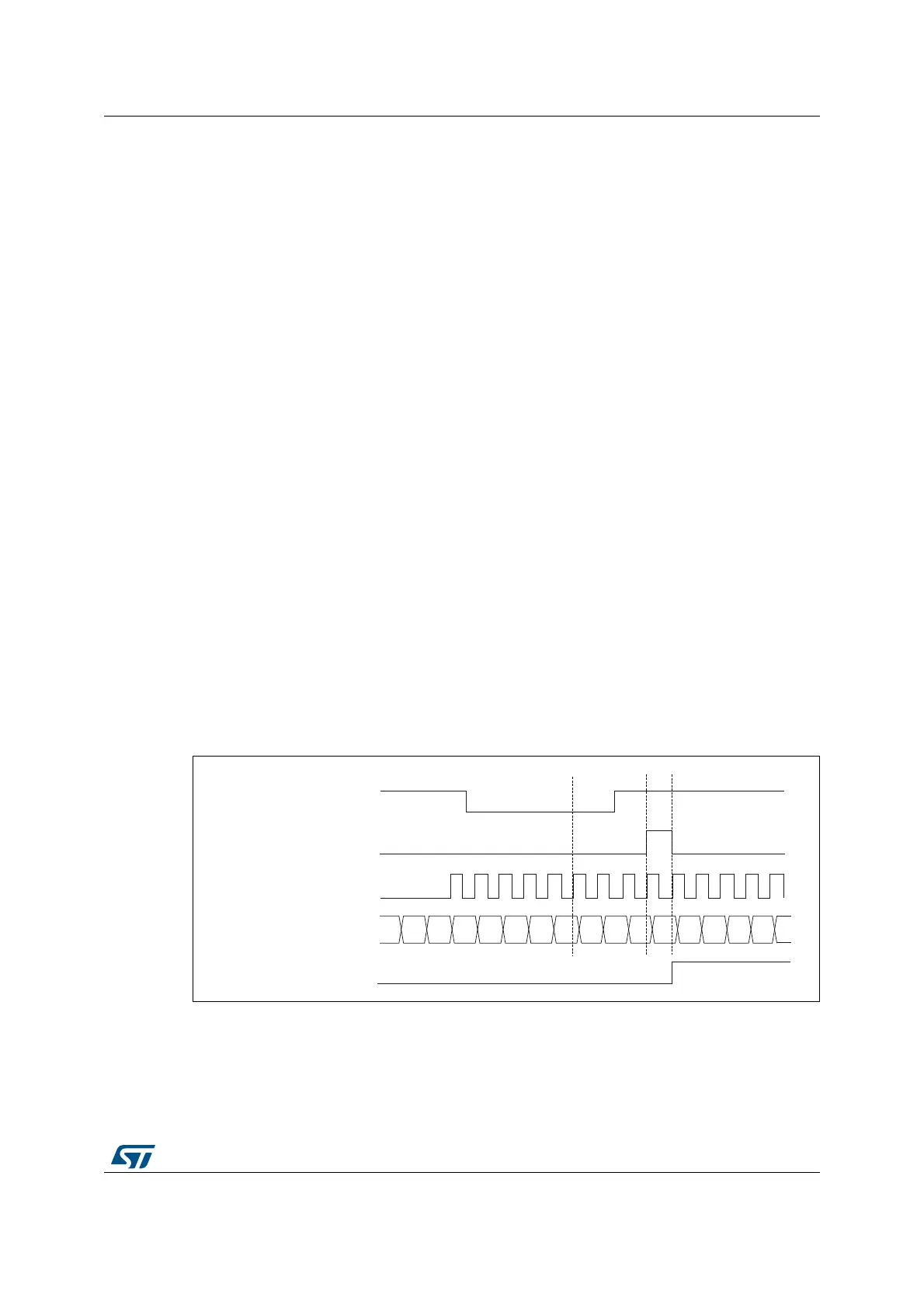

Figure 476. Control circuit in reset mode

MSv62361V1

00

tim_cnt_ck, tim_psc_ck

Counter register

01 02 03 00 01 02 0332 33 34 35 36

UG

tim_ti1

3130

TIF

Loading...

Loading...