High-resolution timer (HRTIM) RM0440

878/2126 RM0440 Rev 4

27.3.6 Up-down counting mode

The HRTIM is natively designed with up-counters. It offers however an operating mode with

up-down counters, also called center-aligned mode.

This mode is enabled using the UDM bit in the HRTIM_TIMxCR2 register. This bit must not

be changed once the timer is operating (TxEN bit set). It is only available for the TIMA..F.

The master timer only works in up-counting mode.

Not all HRTIM features are supported in up-down counting. This section details the

functional differences versus up-counting mode.

The period in HRTIM_PERxR must be preloaded (or static) in up-down mode. It can be

updated only on period event or on counter reset.

The set/reset crossbar programming differs as follows:

The events coming from the timing units are setting/resetting the outputs depending on the

counter up/down direction:

• If the event is enabled in the HRTIM_SETxyR register, it sets the output during up-

counting and reset it during down-counting.

• If the event is enabled in the HRTIM_RSTxyR register, it resets the output during up-

counting and set it during down-counting.

• If the events are enabled both in HRTIM_SETxyR and HRTIM_RSTxyR registers, the

output toggles.

This applies to :

– The timing unit: period, compare 1..4, register update (6 events)

– The master timer: period, compare 1..4, HRTIM synchronization (6 events)

– All other timing units (e.g. timer B..F for timer A): TIMEVNT1..9 (9 events

described in Table 216)

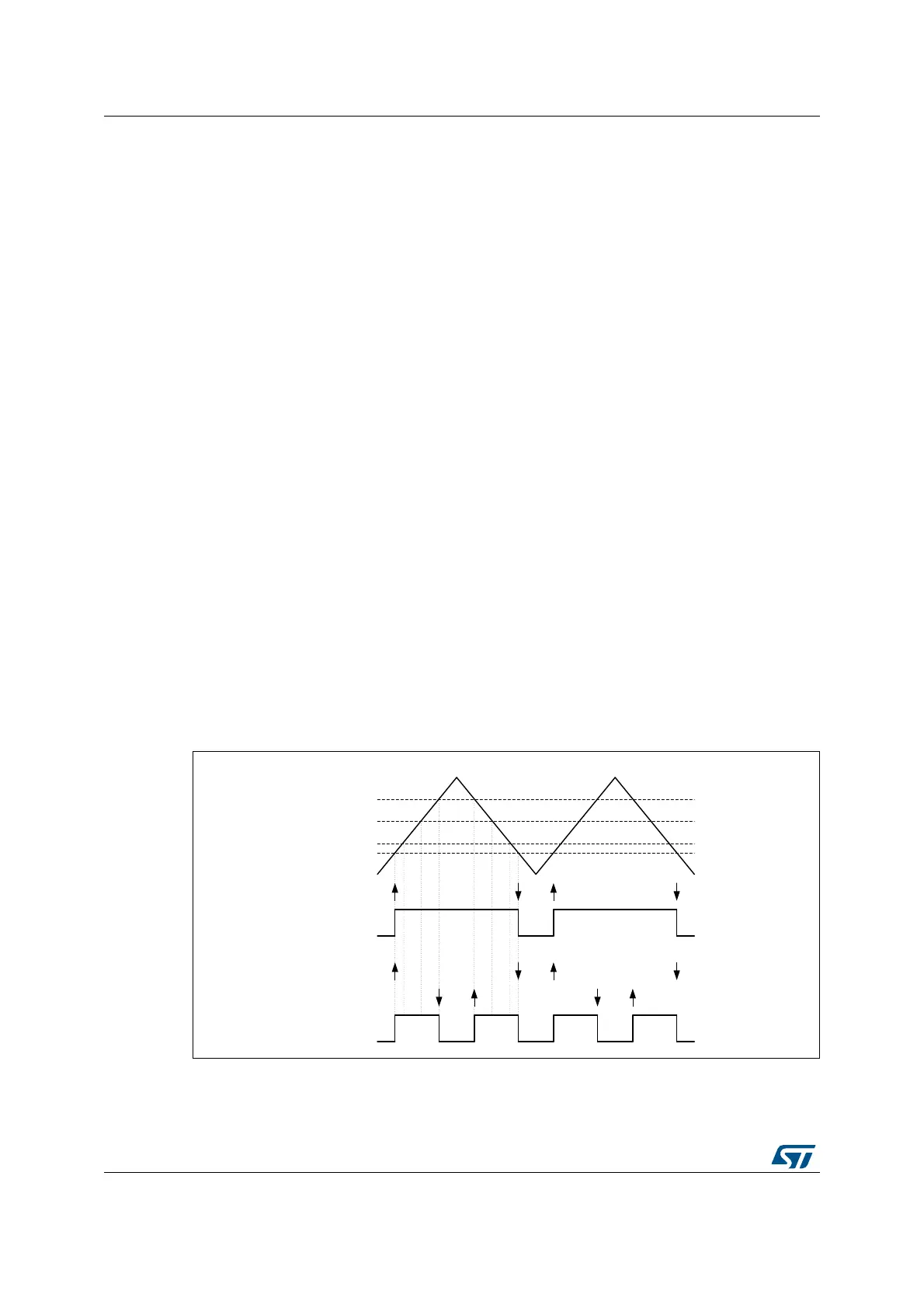

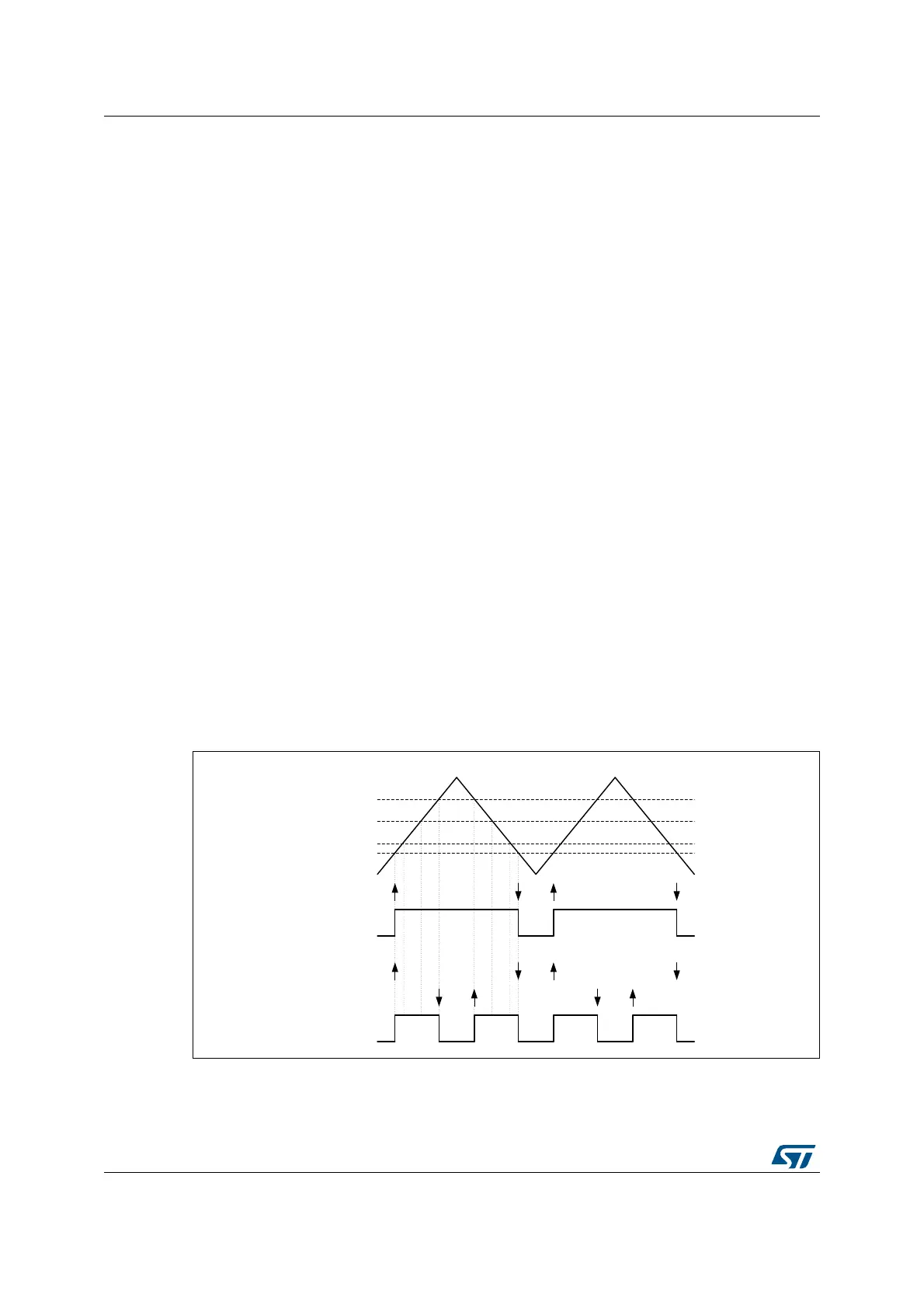

The Figure 205 below shows how to generate basic waveforms.

Figure 205. Basic symmetric waveform in up-down counting mode

MSv45797V2

Counter

HRTIM_CHx1

Set on CMP1

Set on CMP1

Reset on CMP2

HRTIM_CHx2

CMP1

CMP2

CMP3

CMP4

Loading...

Loading...